# Evaluating the Impact of Spike and Flicker Noise in Phase Change Memories

Salin Junsangsri and Fabrizio Lombardi Electrical and Computer Engineering Department Northeastern University Boston, USA

Abstract—This paper presents a simulation-based analysis of spike and flicker noise in a Phase Change Memory (PCM); this investigation is based on HSPICE simulation by taking into account cell-level (with its neighbors) and array-level considerations. State switching phenomena in binary PCM memories are dealt in detail to assess the impact of these two types of noise. It is shown that a lower feature size is of concern for flicker noise in terms of value and percentage variation (while not substantially affecting array-level performance). This paper also shows that spike noise has a radically different behavior: spike noise shows a dependency on the PCM resistance more than the type of state of the PCM. It increases substantially when the amorphous resistance increases and has a nearly constant value when the memory cell is changing to an amorphous state

*Index Terms*—Flicker noise, Spike noise, Phase Change Memory (PCM), Resistance, Frequency.

#### I. INTRODUCTION

The rapid growth and demand on portable storage require non-volatile memory (NVM) operation, Emerging NVM technologies have been proposed in the technical literature; they include the ferro-electrical random access memory (FeRAM), the magneto-resistive RAM (MRAM), and the phase change memory (PCM). PCM is regarded as an excellent candidate for the next generation NVMs due to its high density, fast speed, supply voltage requirements, excellent scaling capability and compatibility with a complementary metal oxide semiconductor (CMOS) fabrication process [1]. Recently, PCM has been proposed for replacing flash memory and DRAM due to its higher reliability/endurance [2] and lower cost than a conventional magnetic recording storage [3]. A PCM is usually fabricated by using a chalcogenide material with crystalline and amorphous phases and resistance state values of several orders of magnitude in difference [4]. However, there has been no study to assess the impact of noise in the operation of a PCM both at memory cell- and array-levels.

This manuscript deals with flicker and spike noise in a memory consisting of 1T1P cells (each cell is made of a MOSFET and a PCM). Flicker noise is one of the extrinsic mechanisms present in electronic devices due to the MOSFET device structure; flicker noise is depended on frequency and Jie Han Electrical and Computer Engineering Department University of Alberta Edmonton, Canada

has been widely analyzed and modeled. Spike noise is the most common noise occurring during state switching.

In this paper, both these types of noise are analyzed at cell- and array-levels by considering different features, such as PCM resistances, MOSFET feature size and operating voltage. Simulation is utilized to assess the effects of noise within the nearest neighbors of a PCM cell as well as the whole memory array. The conditions in binary state switching ('1' to '0' and '0' to '1') correspond to different resistance values in the PCM, hence impacting memory operations at different levels. This paper shows that at lower feature sizes, the flicker noise increases; however, it does not substantially change from cell- to array-levels. The increases in both value and percentage are substantial at a lower feature size; so, the percentage variation of this noise shows a direct relationship with its value. This is significant phenomenon because it could be problematic once smaller feature sizes are employed in memory design. When considering spike noise and switching, this paper shows that the state change from '1' to '0' generates a smaller spike compared to the other case; the spike noise increases substantially when the amorphous resistance increases, but it has a nearly constant value when the memory cell is changing to an amorphous state. Moreover, the variations of spike noise for crystalline and amorphous resistances have similar values, so it is shown that spike noise shows a stronger dependency on the PCM resistance rather than on the type of state of the PCM.

This paper is organized as follows. Section II deals with a brief review of the literature as related to PCM and noise. The PCM cell is assessed in Section III for both flicker and spike noise phenomena; array-level assessments of noise and variation analysis are pursued in Section IV. Section V concludes this manuscript.

#### II. REVIEW

## A. PCM

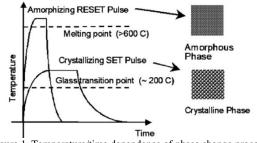

This section reviews different aspects as related to a phase change memory (PCM). As described previously, the phase change memory (PCM) is regarded as one of the most viable candidate for the next generation of non-volatile memories. A PCM relies on the reversible phase transformation of the chalcogenide alloy (e.g.  $Ge_2Sb_2Te_5$ , GST) between the amorphous and the crystalline states. The amorphous state has a high resistance and is commonly referred to as the *reset state*; the crystalline phase has a low resistance and is referred as the *set state* [5]. The PCM device is fabricated by using a thin film chalcogenide layer in contact with a metallic heater. When a programming voltage/current pulse is applied to the PCM, a high current density flows in the resistive heater, thus raising the temperature of the active region as per the Joule effect [5]. The Joule heat generated in this region melts or crystallizes the phase change material to an amorphous, or a crystalline state. The temperature dependence of the phase change (PC) process is shown in Figure 1 [5].

Figure 1. Temperature/time dependence of phase change process [5]

In Figure 1, the pulse with a high amplitude is used to melt and quench the PC element to an amorphous state (Reset State), while the longer pulse with a low amplitude is used to crystallize the PC element (Set State) [5]. Since switching between amorphous and crystalline states is based on the crystalline fraction of the PCM, the electrical resistance of the PCM cell is given as  $R_{PCM} = (1 - C_x)R_a + R_cC_x$  [6] where R<sub>c</sub> and R<sub>a</sub> are the resistances of the PCM when it is fully crystalline and amorphous, respectively. Cx denotes the so-called *crystalline fraction*: when C<sub>x</sub> is zero, then the PCM is fully amorphous; when C<sub>x</sub> is equal to one, the PCM is fully crystalline [1]. If the PCM is in the Reset state (amorphous) and the voltage across the PCM cell is higher than the threshold value (V<sub>th</sub>), then a snapback behavior occurs and the resistance of the PCM is switched to the R<sub>ON</sub> (ON state) value. If the PCM is in the ON state, it will switch back to the OFF state if and only if the voltage across the PCM is less than the so-called ON/OFF Intersection Point [6].

#### B. Noise

Noise is usually defined as an unwanted disturbance that obscures or interfaces with the desired signal. Noise can be classified into four types: thermal noise, low frequency (1/*f*, flicker) noise, generation recombination (G-R) noise, and shot noise [7]. In this paper, flicker and spike noise are considered as applicable to electronic/resistive devices such as found in the 1T1P memory cell and array.

*Flicker Noise:* Flicker noise is a type of noise that is caused by material defects in electronic devices. Since its first experimental demonstration in the early 1960's, it has been extensively analyzed in the technical literature. This noise affects the n-MOSFETs rather than the p-MOSFETs [8], leading possibly to failure of this type of device [9]. In a transistor, flicker noise is one of the extrinsic mechanisms that manifest itself due to the intrinsic structure of the MOSFET [8]. It is also the main cause of phase noise for an oscillator or a phase lock loop; this leads to jitter [10]. There is a correlation between flicker noise and different properties of semiconductor materials and devices; so, this noise serves as a very sensitive measure of defects of semiconductor materials and devices, as well as quality and reliability [11]. It is also know as 1/f noise [12] because flicker noise is present in electronic devices and defines the principal threshold of a small signal at low frequencies. The actual value of flicker noise increases during the lifetime of a transistor [13]; the widely used model of this noise in MOSFETs is given by [14]

flicker noise =

$$\frac{K_f}{C_i \cdot f^{\alpha_f}}$$

where K<sub>f</sub> is an intrinsic process parameter for flicker noise,  $\propto_f$  is an exponent (it usually has a value between 0.8 to 1.2), and C<sub>i</sub> is the gate oxide capacitance (whose value depends on the size of MOSFET) (C<sub>i</sub> = C<sub>ox</sub> · W · L), where C<sub>ox</sub> =  $\frac{\epsilon_{ox}\epsilon_0}{t_{ox}}$ .

*Spike Noise:* Spike noise shows as a high-frequency ripple; it is caused by a switching event [15]. It originates from both material and signal sources. Spike noise is caused by unevenness in circuit elements to exhibit random variations in structural features, such as MOSFET parameters (length, width and depth), as well as doping concentration, mobility of charge carriers and dielectric constant for a device. Moreover, the mobility of charge carriers depends on several secondary effects, such as density of scattering, crystal purity and applied voltage [16]. A spike voltage may cause the failure of a MOSFET and in some cases incorrect switching. In a memory, the characteristics of a spike may affect the read/write process causing errors in some cases [16-18].

#### III. CELL LEVEL EVALUATION

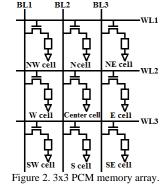

Consider a memory cell consisting of a transistor and a PCM (1T1P). In this cell, the source of the transistor is connected to the PCM, its drain to the Bitline (BL) and its gate to the Wordline (WL) [19]. The neighborhood of a cell (referred to as the *center cell*) consists of 8 cells (Figure 2), hence arranged as a 3x3 neighborhood array.The features of the PCM considered in this manuscript are given in Table 1; for modeling and simulation, each MOSFET has its own noise source (represented by a noise-current generator from drain to source [17]).

| Parameters                                    | Value         |  |

|-----------------------------------------------|---------------|--|

| R <sub>a</sub> (Fully Amorphous Resistance)   | 200k Ohm.     |  |

| R <sub>c</sub> (Fully Crystalline Resistance) | 7k Ohm.       |  |

| Ron (On-Resistance)                           | 1k Ohm.       |  |

| V <sub>hold</sub> (Holding Voltage)           | 0.45 V.       |  |

| V <sub>th</sub> (Threshold Voltage)           | 0.78 V.       |  |

| T <sub>g</sub> (Glass transistion point)      | 473 K         |  |

| -                                             | (200 celsius) |  |

| T <sub>m</sub> (Melting point)                | 873 K         |  |

|                                               | (600 celsius) |  |

Table 1.PCM parameters used in the simulation.

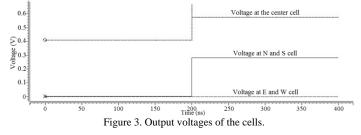

To control a cell, the bitline and wordline voltages are connected to a signal and a controlled voltage value. When the memory cell changes a state, the surrounding cells are affected by a voltage input on both the Bitline and the Wordline. In the simulation, all cells are set to '0'; then the center cell (Figure 2) is set to the on-state (as '1'). The Bitline voltage is affected by the N and S cells, because the Bitline voltage can be sufficiently large to turn the MOSFETs on in both states. The voltage at the Bitline consists of two components: the voltage across the MOSFET and the voltage across the PCM. If the input voltage is set to a proper value, the voltage across the PCM will not be sufficiently large to change the state without the wordline voltage, as the voltage level required to turn on the MOSFET. However, when considering the E and W cells, the wordline voltage is equal to  $V_{dd}$  and the MOSFETs of the E and W cells are on.

Consider Figure 2 and the output voltages of the cells. When the center cell undergoes a state change, noise appears (Figure 3), but it is not sufficiently large to cause an error.

In the nano ranges, both the PCM (as resistive element) and the MOSFET exhibit variability in many parameters, such as length (L), crystalline resistance ( $R_c$ ), amorphous resistance ( $R_a$ ) and threshold voltage ( $V_{th}$ ). Table 2 shows the percentage variation of the different parameters of a MOSFET for various feature sizes [20]. The variations of  $R_c$  and  $R_a$  are fixed to 5% as representing the worst case [17].

| Parameter<br>Feature size | L    | V <sub>th</sub> |

|---------------------------|------|-----------------|

| 16 nm                     | 3%   | 5%              |

| 22 nm                     | 2.5% | 4%              |

| 32 nm                     | 2%   | 3%              |

| 45 nm                     | 2%   | 2%              |

Table 2. Percentage variation of MOSFET parameters at feature size

## A. Flicker Noise

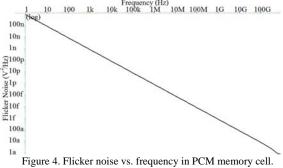

At cell-level, flicker noise is simulated by considering the center cell in Figure 2; Table 3 shows the parameters used in

the simulation of the flicker noise. Figure 4 shows the plot of the flicker noise at a feature size of 32nm for the MOSFET. The PCM changes from state '1' to state '0' with a bias (bitline) voltage of 5V dc (Table 4) and  $1\mu$ V ac for measuring the noise.

| Parameter                              | Value     |  |

|----------------------------------------|-----------|--|

| MOSFET (Level)                         | 32 nm     |  |

| Width (W)                              | 32 nm     |  |

| Length (L)                             | 32 nm     |  |

| t <sub>ox</sub> (Oxide thickness)      | 1 nm      |  |

| $\varepsilon_{ox}$                     | 3.9       |  |

| $\varepsilon_0$                        | 8.854E-12 |  |

| Flicker noise exponent ( $\propto_f$ ) | 1         |  |

Table 3. Device parameters for flicker noise simulation.

The small ac voltage is required for generating the frequency (from 1 to 1T Hz); the wordline is at 0.9V as  $V_{dd}$  of the MOSFET. The simulation results (Figure 4) show that the flicker noise appears at a low frequency and decreases exponentially with frequency (as expected).

| Switching<br>Feature size | <b>'0' to '1'</b> | <b>'1' to '0'</b> |

|---------------------------|-------------------|-------------------|

| 16 nm                     | 3.2V              | 4.3V              |

| 22 nm                     | 3.5V              | 4.7V              |

| 32 nm                     | 3.9V              | 5.0V              |

| 45 nm                     | 4.2V              | 5.3V              |

Table 4 Bias voltage when changing the PCM resistance.

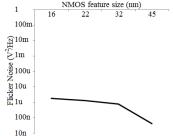

Figure 5 shows that at lower feature sizes, the flicker noise increases too, so possibly becoming of concern for the correct operation of nanoscaled memories.

Figure 5 Flicker noise of 1T1P memory cell vs. feature size

However as the flicker noise is small, the value  $K_f$  is usually given by 0 (as default); however, simulation and the analytical equation for the flicker noise show that  $K_f$  is a sensitive non-zero parameter [14, 21]. The approximate value

of  $K_f$  in a short-channel device at 45nm is given by  $1.62 \times 10^{-24}$ . Table 5 shows its values at different feature sizes.

| Feature size                              | 16nm                   | 22nm                   | 32nm                   | 45nm                   |

|-------------------------------------------|------------------------|------------------------|------------------------|------------------------|

| K <sub>f</sub>                            | 1.35x10 <sup>-23</sup> | 1.59x10 <sup>-23</sup> | 1.76x10 <sup>-23</sup> | 1.62x10 <sup>-24</sup> |

| Table 5. $K_f$ at different feature sizes |                        |                        |                        |                        |

#### B. Spike Noise

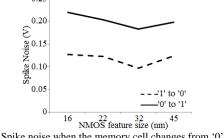

Spike noise may occur when the input voltage switches from one state to the other. The signal at the wordline is given as a square voltage from '0' to  $V_{dd}$  of the MOSFET under consideration; this is different from the simulation setup for the flicker noise. Spike noise is considered with respect to the feature size of a MOSFET and the value of R<sub>a</sub>. The noise is measured for both state switching conditions ('1' to '0' and '0' to '1') in a cell. State switching generates a spike noise due to the changing voltage (that may also affect the operation of the cell [17]). To reduce the effect on other neighboring cells and any additional noise, the bitline voltage is given in Table 4 to change the data in the memory cell and state of the MOSFET (with same width and length), while the wordline voltage is given by a square signal (so of amplitude between 0 to V<sub>dd</sub>). The plot of spike noise versus feature size is shown in Figure 6 for both cases of state switching. 0.25

Figure 6.Spike noise when the memory cell changes from '0' to '1' and from '1' to '0' vs. feature size

When considering spike noise and switching, the state change from '1' to '0' generates a smaller spike compared to the other case. The simulation results for the spike noise in Figure 6 show that for switching from '1' to '0' requires a larger bias voltage and moreover, the voltage across the PCM at the reset state ('0') is higher than for the set state ('1').

The voltage for a state changes from '0' to '1' is lower than for '1' to '0', because it requires a lower voltage to change the data. The voltage across the PCM when its data is '1' has a smaller value, this causes a spike noise that is lower than for '0', i.e. the switching from '0' to '1' causes a larger spike noise than for the other case. Moreover, spike noise also depends on other parameters, such as the value of R<sub>a</sub>. Figure 7 shows the spike noise when varying R<sub>a</sub>. When the amorphous resistance R<sub>a</sub> increases (while maintaining all other parameters constant), the spike noise increases substantially. When simulating this case, the crystalline fraction decreases with an increase of  $R_a$ ; so, the PCM becomes less crystalline if the value of  $R_a$  is higher. When the frequency (f) increases there is no sufficient time to change the PCM from the amorphous to the fully crystalline states. Furthermore, the spike noise occurs only at the switching time of the PCM, thus a change in frequency does not affect the spike noise.

Figure 8 shows the value of spike noise of a 1T1P cell when the state of the PCM is changed from '0' to '1' at different values of  $V_{dd}$ . Only this state change is considered, because this state produces the highest value of spike noise.

In this simulation, a feature size of 32nm is used (the nominal value of  $V_{dd}$  is 0.9V); the results show that between 0.5V and 0.8V, the voltage is not high enough to turn on the gate of the transistor, so the voltage at the bitline will not affect the PCM of the memory cell. The values between 0.9V and 2V correspond to a voltage range that can turn the PCM on and change its state from '0' to '1'; however, the cell cannot write '1' at the higher voltage, because these high values of voltage require higher temperatures to the PCM, so a '0' rather than '1' is best applicable as erroneous state switching.

#### IV. ARRAY LEVEL EVALUATION

In this section, the 1T1P cell is considered within a square array of dimension n; the effects of flicker and spike noise are then considered within an nxn memory array to assess the impact when different operational features are varied.

#### A. Flicker Noise

The same parameters as outlined previously for cell-level simulation are considered; simulation has shown that the flicker noise does not substantially change at array-level, so the same results as presented previously at cell-level are also applicable. This implies that flicker noise is only a concern with the cell neighbors (as shown in Figure 2 previously).

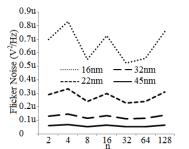

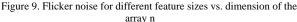

The flicker noise variation is simulated by a Poisson distribution that takes into considerations many physical parameters [13]. Figure 9 shows the flicker noise at different feature sizes. Simulation is pursued under the condition that the initial state of the PCM is the fully crystalline state, and the write voltage is set to a value that changes the PCM to be more amorphous.

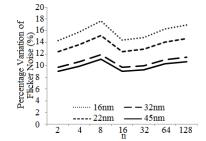

Figure 10. Percentage variation of flicker noise across PCM for different feature sizes vs. dimension of the array n

However, the flicker noise will be smaller for the initial opposite state (i.e. fully amorphous state) and a write voltage to have a more crystalline state, due to the smaller write voltage. The trend of the flicker noise in Figure 9 shows that at a lower feature size, the flicker noise increases (both in value and percentage); this is caused by the smaller values in MOSFET parameters due to scaling. Figure 10 shows the percentage variation of the flicker noise when the parameters are simulated by Monte Carlo. Moreover, the percentage variation of this noise shows a direct relationship with noise value; this is significant because it shows that it may be problematic once smaller feature sizes are employed in memory design.

# B. Spike Noise

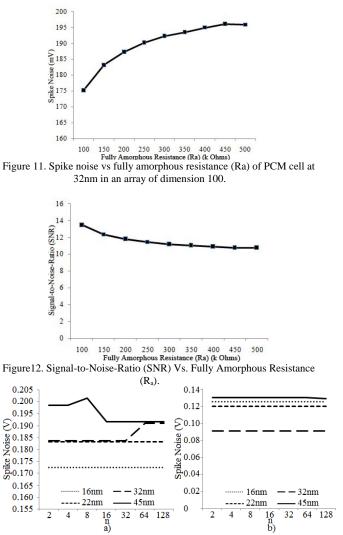

In this section, spike noise is considered at a feature size of 32nm for an nxn PCM memory array. It is well known that spike noise and the crystalline fraction  $(C_x)$  are not dependent on array size, hence, the impact of changing the fully amorphous resistance is considered. Figure 11 shows the results; spike noise increases rather modestly in the memory array at a 32nm feature size; moreover, the spike noise at different values of  $R_a$  is inversely proportional to the Signal-to-Noise Ratio (SNR), because the SNR decreases for an increasing  $R_a$  (Figure 12). Therefore,  $R_a$  can take a large value while still keeping a nearly constant SNR. Even though not specifically addressed in this manuscript, this feature confirms that a greater resistance range permits a multi-level implementation in a memory.

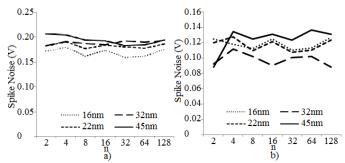

Figures 13, 14 and 15 show the spike noise when the dimension n is varied at different feature sizes and under different conditions; the simulation results are pursued when the state changes occur for either crystalline or amorphous. Figure 13 shows the spike noise when the feature size is varied versus n. A comparison between Figures 13(a) and

13(b) confirms that the change from the amorphous to the crystalline states results in a higher spike noise. This difference is related to the change in PCM resistance due to state switching.

Figure 13. Spike noise when changing state to a) crystalline b) amorphous at different feature size vs. n.

Figure 14. Spike noise when changing state to a) crystalline b) amorphous at different feature size vs. n.

Figure 14 shows the spike noise when simulation takes into account the variations in MOSFET (Table 2) and PCM resistance. The trends are similar to Figure 13, even though now the spike noise is not as constant as in Figure 13(b).

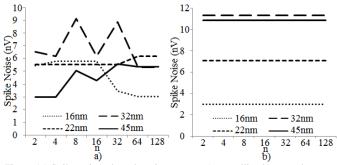

Figure 15. Spike noise when changing state to a) crystalline b) amorphous at variation of the threshold voltage  $(V_{th})$  vs. n.

Figure 15 shows the simulation results when only the threshold voltage is changed (as in Table 2). A variation in  $V_{th}$  does not cause a significant amount of spike noise; these simulation results also show that also in this case, spike noise has a nearly constant value when the memory cell is changing to the amorphous state.

#### V. CONCLUSION

This paper has presented a simulation-based analysis of spike and flicker noise in a Phase Change Memory (PCM); this investigation was pursued using HSPICE simulation. In this paper, both these types of noise have been analyzed at cell- and array-levels by considering different features, such as PCM resistances, MOSFET feature size and operating voltage. The following conclusions can be drawn from the simulation results:

• *Flicker noise:* this noise is inversely proportional to MOSFET feature sizes, but for PCM memories, it does not substantially change from cell- to array-levels. The increases in both value and percentage are substantial at a lower feature size and the percentage variation of this noise shows a direct relationship with its value. As memory technology moves to the nanoscales, this phenomenon could be of serious concern.

• *Spike noise:* when considering switching, this paper has shown that the state change from '1' to '0' generates a smaller spike compared to the other case; the spike noise increases substantially when the amorphous resistance increases, but it has a nearly constant value when the memory cell is changing to an amorphous state. Moreover, the variations of spike noise for crystalline and amorphous resistances have similar values, so it has been shown that spike noise has a stronger dependency on the PCM resistance rather than on the type of state of the PCM.

Current research deals with assessing the effects of thermal noise; note that thermal noise in a PCM is mostly due to an external component (i.e, the heater) for a state transition (as shown previously in Figure 1).

#### VI. REFERENCES

- C.Dao-Lin, S. Zhi-Tang, L. Xi, C. Hou-Peng, C. Xiao-Gang "A Compact SPICE Model with Verilog-A for Phase Change Memory" *Chin. Phys. Lett.* Vol.28, No.1 (2011) 018501.

- [2] G. W. Burr, M. J. Breitwisch, M. Franceschini, D Garetto, K. Gopalakrishnan1, B. Jackson1, B. Kurdi, C. Lam, L. A. Lastras, A. Padilla, B. Rajendran, S. Raoux, R. S. Shenoy "Phase Change Memory technology" *Journal of Vacuum Science and Technology B.*, vol. 28, issue. 2, pp. 223-262, March 2010

- [3] W. Xu, T. Zhang "A Time-Aware Fault Tolerance Scheme to Improve Reliability of Multilevel Phase-Change Memory in the Presence of Significant Resistance Drift" *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Vol. 19, No. 8, pp. 1357-1365, August 2011.

- [4] A. L. Lacaita, "Phase change memories: State-of-the-art, challenges and perspectives," *Solid-State Electron.*, vol. 50, pp. 24–31, Jan. 2006

- [5] X.Q. Wei, L.P. Shi, R. Walia, T.C. Chong, R. Zhao, X.S. Miao, B.S. Quek "HSPICE Macromodel of PCRAM for Binary and Multilevel Storage" *IEEE Trans. Electron Devices.* Vol. 53, No.1 Jan 2006

- [6] P. Junsangsri, F. Lombardi "A New Comprehensive Model of a Phase Change Memory (PCM) Cell", *IEEE Transactions on Nanotechnology*, vol 13, no. 6, pp. 1213-1225, 2014.

- [7] C. D. Motchenbacher, J. A. Connelly "Low Noise Electronic System Design" New York: Wiley, 1993, pp. 8–32

- [8] Renuka P. Jindal "Compact Noise Models for MOSFETs" IEEE Transactions on Electron Devices, Vol. 53, No. 9, pp. 2051-2061, September 2006

- [9] M. Hanson "Achieving Accurate On-Wafer Flicker Noise Measurement Through 30 MHZ" Cascade Microtech, Inc., May 2009 [Online]. Available: <u>www.cascademicrotech.com</u>

- [10] H. Belahrach, M. Karim, J. Farre "Noise characterization in CMOS APS images for highly integrated imaging systems" Microelectronics, 2001. ICM2001, pp.31-34, Oct 2001

- [11] S. Mohammadi and D. Pavlidis, "A nonfundamental theory of lowfrequency noise in semiconductor devices," *IEEE Trans. Electron Devices*, vol. 47, no. 11, pp. 2009–2017, Nov. 2000

- [12] F. A. Levinzon "Measurement of Low-Frequency Noise of Modern Low-Noise Junction Field Effect Transistors" *IEEE Transactions on Instrumentation and Measurement*, Vol. 54, No. 6, pp. 2427-2432, December 2005

- [13] M. Erturk "The bias dependence of CMOS 1/f noise statistics, its modeling and impact on RF circuits" Dissertation, The University of Vermont, May 2008. [Online]. Available: <u>https://library.uvm.edu/jspui/bitstream/123456789/125/1/met e%20erturk\_2008.pdf</u>

- [14] M. Manghisoni, L. Ratti, V. Re, V. Speziali, G. Traversi "Low-noise Design Issues for Analog Front-end Electronics in 130 nm and 90 nm CMOS Technologies" 12<sup>th</sup> Workshop on Electronics For LHC and Future Experiments, Valencia Spain, pp. 483-487, 25-29 September 2006

- [15] H. Asahara, T. Kousaka "Qualitative analysis of an interrupted electric circuit with spike noise" *International Journal of Circuit Theory and Applications*, Vol. 39, Issue 11, pp. 1177-1187, November2011

- [16] J.T. Wallmark "Noise Spikes in Digital VLSI Circuits" IEEE Transactions on Electron Devices, Vol. Ed 2-9, No. 3, pp. 451-458, March 1982

- [17] W. Wei "Novel Paradigms and Designs of Nanometric Memories", PhD Dissertation, Northeastern University 2015.

- [18] U. Melia, F. Claria, M. Vallverdu, P. Caminal "Removal of Peak and Spike Noise in EEG Signals Based on the Analytic Signal Magnitude" 34<sup>th</sup> Annual International Conference of the IEEE EMBS, San Diego, California USA, pp. 3523-3526, 28 August – 1 September, 2012.

- [19] M.G. Mohammad "Fault model and test procedure for phase change memory" *IET Computers & Digital Techniques*, Vol.5, No.4, pp.263-270, July 2011.

- [20] A. Rubio, J. Figueras, I. Vatajlu, R. Canal "Process variability in sub-16nm bulk CMOS technology, 2012. [Online]. Available http://hdl. handle.net/2117/15667

- [21] D. Xie, M. Cheng, L. Forbes "SPICE Models for Flicker Noise in n-MOSFETs from Subthreshold to Strong Inversion" *IEEE Transactions* on Computer-Aided Design of Integrated Circuits and Systems, Vol. 19, No. 11, pp. 1293-1303, November 2000