Page 1 of 13

# Design and Analysis of Approximate Compressors for Multiplication

# A. Momeni, J. Han, Member, P.Montuschi, Senior Member and F. Lombardi, Fellow

Abstract—Inexact (or approximate) computing is an attractive paradigm for digital processing at nanometric scales. Inexact computing is particularly interesting for computer arithmetic designs. This paper deals with the analysis and design of two new approximate 4-2 compressors for utilization in a multiplier. These designs rely on different features of compression, such that imprecision in computation (as measured by the error rate and the so-called normalized error distance) can meet with respect to circuit-based figures of merit of a design (number of transistors, delay and power consumption). Four different schemes for utilizing the proposed approximate compressors are proposed and analyzed for a Dadda multiplier. Extensive simulation results are provided and an application of the approximate multipliers to image processing is presented. The results show that the proposed designs accomplish significant reductions in power dissipation, delay and transistor count compared to an exact design; moreover, two of the proposed multiplier designs provide excellent capabilities for image multiplication with respect to average normalized error distance and peak signal-to-noise ratio (more than 50dB for the considered image examples).

Index Terms—Compressor, Dadda Multiplier, Inexact Computing, Approximate Circuits

#### I. INTRODUCTION

computer arithmetic OST applications are implemented using digital logic circuits, thus operating with a high degree of reliability and precision. However, many applications such as in multimedia and image processing can tolerate errors and imprecision in computation and still produce meaningful and useful results. Accurate and precise models and algorithms are not always suitable or efficient for use in these applications. The paradigm of inexact computation relies on relaxing fully precise and completely deterministic building modules when for example, designing energy-efficient systems. This allows imprecise computation to redirect the existing design process of digital circuits and systems by taking advantage of a decrease in complexity and cost with possibly a potential increase in performance and power efficiency. Approximate (or *inexact*) computing relies on using this property to design simplified, yet approximate circuits operating at higher performance and/or lower power consumption compared with precise (exact) logic circuits [1].

Addition and multiplication are widely used operations in computer arithmetic; for addition full-adder cells have been extensively analyzed for approximate computing [2-4]. [1] has compared these adders and proposed several new metrics for evaluating approximate and probabilistic adders with respect to unified figures of merit for design assessment for inexact computing applications. For each input to a circuit, the error distance (ED) is defined as the arithmetic distance between an erroneous output and the correct one [1]. The mean error distance (MED) and normalized error distance (NED) are proposed by considering the averaging effect of multiple inputs and the normalization of multiple-bit adders. The NED is nearly invariant with the size of an implementation and is therefore useful in the reliability assessment of a specific design. The tradeoff between precision and power has also been quantitatively evaluated in [1].

However, the design of approximate multipliers has received less attention. Multiplication can be thought as the repeated sum of partial products; however, the straightforward application of approximate adders when designing an approximate multiplier is not viable, because it would be very inefficient in terms of precision, hardware complexity and other performance metrics. Several approximate multipliers have been proposed in the literature [4] [5] [6] [7]. Most of these designs use a truncated multiplication method; they estimate the least significant columns of the partial products as a constant. In [4], an imprecise array multiplier is used for neural network applications by omitting some of the least significant bits in the partial products (and thus removing some adders in the array). A truncated multiplier with a correction constant is proposed in [5]. For an  $n \times n$  multiplier, this design calculates the sum of the n+k most significant columns of the partial products and truncates the other n-kcolumns. The n+k bit result is then rounded to n bits. The reduction error (i.e. the error generated by truncating then-k least significant bits) and rounding error (i.e. the error generated by rounding the result to *n* bits) are found in the next step. The correction constant (n+k bits) is selected to be as close as possible to the estimated value of the sum of these errors to reduce the error distance.

A truncated multiplier with constant correction has the maximum error if the partial products in the *n*-*k* least significant columns are all *ones* or all *zeros*. A variable correction truncated multiplier has been proposed in [6]. This method changes the correction term based on column *n*-*k*-*1*. If all partial products in column*n*-*k*-*1* are *one*, then the correction term is increased. Similarly, if all partial products in this column are *zero*, the correction term is decreased.

In [7], a simplified (and thus inaccurate)  $2x^2$  multiplier block is proposed for building larger multiplier arrays. In the design of a fast multiplier, compressors have been widely used

A Momeni and F. Lombardi are with the Department of Electrical and Computer Engineering, Northeastern University, Boston, MA 02115, USA; {lombardi@ece.neu.edu, momeni.a@husky.neu.edu}. J. Han is with the Department of Electrical and Computer Engineering, University of Alberta, Edmonton, Canada; {jhan8@ualberta.ca}, P. Montuschi is with the Department of Control and Computer Engineering, Politecnico di Torino, Turin, Italy;{paolo.montuschi@polito.it)

[8-10] to speed up the partial product reduction tree and decrease power dissipation. Optimized designs of 4-2 exact compressors have been proposed in [8, 11 - 16]. [17] [18] have also considered compression for approximate multiplication. In [17], an approximate signed multiplier has been proposed for use in arithmetic data value speculation (AVDS); multiplication is performed using the Baugh-Wooley algorithm. However, no new design is proposed for the compressors for the inexact computation. Designs of approximate compressors have been proposed in [18]; however, these designs do not target multiplication. It should be noted that the approach of [7] improves over [17] [18] by utilizing a simplified multiplier block that is amenable to approximate multiplication.

1

2

3

4

5

6

7

8

9

10

11

12

13 14

15

16 17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44 45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

Initially in this paper, two novel approximate 4-2 compressors are proposed and analyzed. It is shown that these simplified compressors have better delay and power consumption than the optimized (exact) 4-2 compressor designs found in the technical literature [8]. These approximate compressors are then used in the restoration module of a Dadda multiplier; four different schemes are proposed for inexact multiplication. Extensive simulation results are provided at circuit-level for figures of merit, such as delay, transistor count, power dissipation, error rate and normalized error distance under CMOS feature sizes of 32, 22 and 16 nm. The application of these multipliers to image processing is then presented. The results of two examples of multiplication of two images are reported; these results show that the third and fourth approximate multipliers yield an output product image that has a very high quality and resemblance to the image generated by an exact multiplier, i.e. excellent values for the average NED and the Peak Signal-to-Noise Ratio (PSNR) are found (for the PSNR more than 50db). The analysis and simulation results show that the proposed approximate designs for both the compressor and the multiplier are viable candidates for inexact computing.

This paper is organized as follows. Section 2 is a review of existing schemes for (exact) compressors. The two new designs of an approximate 4-2 compressor are presented in Section 3.Multiplication and four different approximate multipliers are proposed in Section 4. Simulation results for the approximate compressors and multipliers are provided in Section 5. The application of the proposed approximate multipliers to image processing is presented in Section 6. Section 7 concludes the manuscript.

#### II. EXACT COMPRESSORS

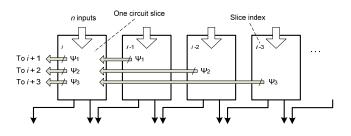

The main goal of either multi-operand carry-save addition or parallel multiplication is to reduce *n* numbers to two numbers; therefore, *n*-2 compressors (or *n*-2 counters) have been widely used in computer arithmetic. A*n*-2 compressor (Figure 1) is usually a slice of a circuit that reduces *n* numbers to two numbers when properly replicated. In slice *i* of the circuit, the *n*-2 compressor receives *n* bits in position *i* and one or more carry bits from the positions to the right, such as i - 1or i - 2. It produces two output bits in positions *i* and i + 1 and one or more carry bits into the higher positions, such as i + 1 or i + 2. For the correct operation of the circuit shown in Figure 1, the following inequality must be satisfied

$n + \psi_1 + \psi_2 + \psi_3 + \dots \le 3 + 2\psi_1 + 4\psi_2 + 8\psi_3 + \dots$ (1)

Figure 1.Schematic diagram of *n*-2 compressors in a multi operand addition circuit [13]

Where  $\psi_j$  denotes the number of carry bits from slice *i*to slice *i*+*j*.

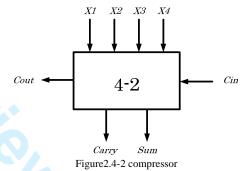

A widely used structure for compression is the 4-2 compressor; a 4-2 compressor (Figure 2) can be implemented with a carry bit between adjacent slices ( $\psi_1 = 1$ ). The carry bit from the position to the right is denoted as  $c_{in}$  while the carry bit into the higher position is denoted as  $c_{out}$ . The two output bits in positions *i* and *i* + 1 are also referred to as the *sum* and *carry* respectively.

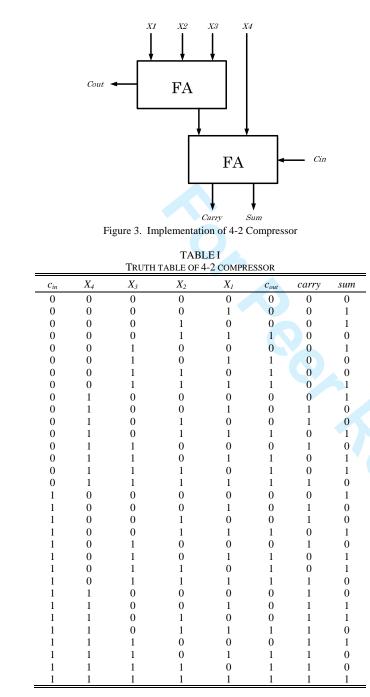

The following equations give the outputs of the 4-2 compressor, while Table 1 shows its truth table.

| $Sum = x1 \oplus x2 \oplus x3 \oplus x4 \oplus Cin$                                       | (2) |

|-------------------------------------------------------------------------------------------|-----|

| $Cout = (x1 \oplus x2)x3 + \overline{(x1 \oplus x2)}x1$                                   | (3) |

| Carry =                                                                                   |     |

| $(x1 \oplus x2 \oplus x3 \oplus x4)Cin + \overline{(x1 \oplus x2 \oplus x3 \oplus x4)}x4$ | (4) |

The common implementation of a 4-2 compressor is accomplished by utilizing two full-adder (FA) cells (Figure 3) [8]. Different designs have been proposed in the literature for 4-2 compressor [8, 11-16].

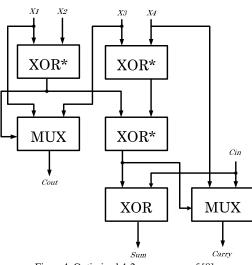

Figure 4 shows the optimized design of an exact4-2 compressor based on the so-called XOR-XNOR gates [8]; a XOR-XNOR gate simultaneously generates the XOR and XNOR output signals. The design of [8] consists of three XOR-XNOR (denoted by XOR<sup>\*</sup>) gates, one XOR and two 2-1 MUXes. The critical path of this design has a delay of  $3\Delta$ , where  $\Delta$  is the unitary delay through any gate in the design.

#### III. PROPOSED APPROXIMATE COMPRESSORS

In this section, two designs of an approximate compressor are proposed. Intuitively to design an approximate 4-2 compressor, it is possible to substitute the exact full-adder cells in Figure3 by an approximate full-adder cell (such as the first design proposed in [2]). However, this is not very efficient, because it produces at least 17 incorrect results out of 32 possible outputs, i.e. the error rate of this inexact compressor is more than 53% (where the *error rate* is given by the ratio of the number of erroneous outputs over the total number of outputs). Two different designs are proposed next to reduce the error rate; these designs offer significant performance improvement compared to an exact compressor with respect to delay, number of transistors and power consumption.

#### Figure4. Optimized 4-2 compressor of [8]

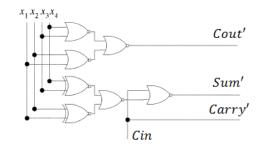

#### A. Design 1

As shown in Table I, the *carry* output in an exact compressor has the same value of the input  $c_{in}$  in 24 out of 32 states. Therefore, an approximate design must consider this feature. In Design 1, the *carry* is simplified to  $c_{in}$  by changing the value of the other 8 outputs.

$$Carry' = Cin \tag{5}$$

Since the *Carry* output has the higher weight of a binary bit, an erroneous value of this signal will produce a difference value of two in the output. For example, if the input pattern is "01001" (row 10 of Table II), the correct output is "010" that is equal to 2. By simplifying the carry output to  $c_{in}$ , the approximate compressor will generate the "000" pattern at the output (i.e. a value of 0). This substantial difference may not be acceptable; however, it can be compensated or reduced by simplifying the  $c_{out}$  and sum signals. In particular, the simplification of sum to a value of 0 (second half of Table II) reduces the difference between the approximate and the exact outputs as well as the complexity of its design. Also, the presence of some errors in the sum signal will results in a reductions of the delay of producing the approximate sum and the overall delay of the design (because it is on the critical path).

$$Sum' = \overline{Cin}(\overline{x1 \oplus x2} + \overline{x3 \oplus x4}) \tag{6}$$

In the last step, the change of the value of  $c_{out}$  in some states, may reduce the error distance provided by approximate *carry* and *sum* and also more simplification in the proposed design.

$$Cout' = (\overline{x1x2} + \overline{x3x4}) \tag{7}$$

Although the above mentioned simplifications of *carry* and *sum* increase the error rate in the proposed approximate compressor, its design complexity and therefore the power consumption are considerably decreased. This can be realized by comparing (2)-(4) and (5)-(7).Table II shows the truth table of the first proposed approximate compressor. It also shows the difference between the inexact output of the proposed approximate compressor. As shown in Table II, the proposed design has 12 incorrect outputs out of 32 outputs (thus yielding an error rate of 37.5%). This is less than the error rate using the best approximate full-adder cell of [2].

|     | TRU            |    | RI F OF | THF FI | TABLE | E II<br>OXIMATE 4 | -2 COMPRI | FSSOR      |

|-----|----------------|----|---------|--------|-------|-------------------|-----------|------------|

| Cin | X <sub>4</sub> | X3 | $X_2$   | $X_I$  | Cout' | carry'            | sum'      | Difference |

| 0   | 0              | 0  | 0       | 0      | 0     | 0                 | 1         | 1          |

| 0   | 0              | 0  | 0       | 1      | 0     | 0                 | 1         | 0          |

| 0   | 0              | 0  | 1       | 0      | 0     | 0                 | 1         | 0          |

| 0   | 0              | 0  | 1       | 1      | 0     | 0                 | 1         | -1         |

| 0   | 0              | 1  | 0       | 0      | 0     | 0                 | 1         | 0          |

| 0   | 0              | 1  | 0       | 1      | 1     | 0                 | 0         | 0          |

| 0   | 0              | 1  | 1       | 0      | 1     | 0                 | 0         | 0          |

| 0   | 0              | 1  | 1       | 1      | 1     | 0                 | 1         | 0          |

| 0   | 1              | 0  | 0       | 0      | 0     | 0                 | 1         | 0          |

| 0   | 1              | 0  | 0       | 1      | 1     | 0                 | 0         | 0          |

| 0   | 1              | 0  | 1       | 0      | 1     | 0                 | 0         | 0          |

| 0   | 1              | 0  | 1       | 1      | 1     | 0                 | 1         | 0          |

| 0   | 1              | 1  | 0       | 0      | 0     | 0                 | 1         | -1         |

| 0   | 1              | 1  | 0       | 1      | 1     | 0                 | 1         | 0          |

| 0   | 1              | 1  | 1       | 0      | 1     | 0                 | 1         | 0          |

| 0   | 1              | 1  | 1       | 1      | 1     | 0                 | 1         | -1         |

| 1   | 0              | 0  | 0       | 0      | 0     | 1                 | 0         | 1          |

| 1   | 0              | 0  | 0       | 1      | 0     | 1                 | 0         | 0          |

| 1   | 0              | 0  | 1       | 0      | 0     | 1                 | 0         | 0          |

| 1   | 0              | 0  | 1       | 1      | 0     | 1                 | 0         | -1         |

| 1   | 0              | 1  | 0       | 0      | 0     | 1                 | 0         | 0          |

| 1   | 0              | 1  | 0       | 1      | 1     | 1                 | 0         | 1          |

| 1   | 0              | 1  | 1       | 0      | 1     | 1                 | 0         | 1          |

| 1   | 0              | 1  | 1       | 1      | 1     | 1                 | 0         | 0          |

| 1   | 1              | 0  | 0       | 0      | 0     | 1                 | 0         | 0          |

| 1   | 1              | 0  | 0       | 1      | 1     | 1                 | 0         | 1          |

| 1   | 1              | 0  | 1       | 0      | 1     | 1                 | 0         | 1          |

| 1   | 1              | 0  | 1       | 1      | 1     | 1                 | 0         | 0          |

| 1   | 1              | 1  | 0       | 0      | 0     | 1                 | 0         | -1         |

| 1   | 1              | 1  | 0       | 1      | 1     | 1                 | 0         | 0          |

| 1   | 1              | 1  | 1       | 0      | 1     | 1                 | 0         | 0          |

| 1   | 1              | 1  | 1       | 1      | 1     | 1                 | 0         | -1         |

(5)-(7) are the logic expressions for the outputs of the first design of the approximate 4-2 compressor proposed in this manuscript.

The gate level structure of the first proposed design (Figure 6) shows that the critical path of this compressor has still a delay of  $3\Delta$ , so it is the same as for the exact compressor of Figure 5. However, the propagation delay through the gates of this design is lower than the one for the exact compressor. For example, the propagation delay in the *XOR*\* gate that generates both the *XOR* and *XNOR* signals in [8], is higher than the delay through a *XNOR* gate of the proposed design. Therefore, the critical path delay in the proposed design is lower than in the exact design and moreover, the total number of gates in the proposed design is significantly less than that in the optimized exact compressor of [8].

## B. Design 2

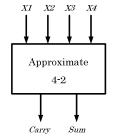

A second design of an approximate compressor is proposed to further increase performance as well as reducing the error rate. Since the *carry* and  $c_{out}$  outputs have the same weight, the proposed equations for the approximate *carry* and  $c_{out}$  in the previous part can be interchanged. In this new design, *carry* uses the right hand side of (7) and  $c_{out}$  is always equal to  $c_{in}$ ; since  $c_{in}$  is zero in the first stage,  $c_{out}$  and  $c_{in}$  will be zero in all stages. So,  $c_{in}$  and  $c_{out}$  can be ignored in the hardware design. Figure 7shows the block diagram of this approximate 4-2 compressor and the expressions below describe its outputs.

$$Sum' = (\overline{x1 \oplus x2} + \overline{x3 \oplus x4})$$

$$Carry' = (\overline{x1x2} + \overline{x3x4})$$

(8)

(9)

Figure 6. Gate level implementation of Design 1

Figure7. Approximate 4-2 compressor, Design 2

Note that (9) is the same as (7) and (8) is the same as (6) for  $c_{in}=0$ . Figure 8 shows the gate level implementation of the second proposed design. The delay of the critical path of this approximate design is 2 $\Delta$ , so it is 1 $\Delta$  less than the previous designs; moreover, a further reduction in the number of gates is accomplished.

Figure 8. Gate level implementation of Design 2

Table III shows the truth table of the second approximate design for a 4-2 compressor; this Table also shows the difference between the exact decimal value of the addition of the inputs and the decimal value of the outputs produced by the approximate compressor. For example when all inputs are

1, the decimal value of the addition of the inputs is 4. However, the approximate compressor produces a 1 for the *carry* and *sum*. The decimal value of the outputs in this case is 3; Table II shows that the difference is -1.

TABLE III

| $X_4$ | $X_3$ | $X_2$ | $X_I$ | carry' | sum' | difference |

|-------|-------|-------|-------|--------|------|------------|

| 0     | 0     | 0     | 0     | 0      | 1    | 1          |

| 0     | 0     | 0     | 1     | 0      | 1    | 0          |

| 0     | 0     | 1     | 0     | 0      | 1    | 0          |

| 0     | 0     | 1     | 1     | 0      | 1    | -1         |

| 0     | 1     | 0     | 0     | 0      | 1    | 0          |

| 0     | 1     | 0     | 1     | 1      | 0    | 0          |

| 0     | 1     | 1     | 0     | 1      | 0    | 0          |

| 0     | 1     | 1     | 1     | 1      | 1    | 0          |

| 1     | 0     | 0     | 0     | 0      | 1    | 0          |

| 1     | 0     | 0     | 1     | 1      | 0    | 0          |

| 1     | 0     | 1     | 0     | 1      | 0    | 0          |

| 1     | 0     | 1     | 1     | 1      | 1    | 0          |

| 1     | 1     | 0     | 0     | 0      | 1    | -1         |

| 1     | 1     | 0     | 1     | 1      | 1    | 0          |

| 1     | 1     | 1     | 0     | 1      | 1    | 0          |

| 1     | 1     | 1     | 1     | 1      | 1    | -1         |

This design has therefore 4 incorrect outputs out of 16 outputs, so its error rate is now reduced to 25%. This is a very positive feature, because it shows that on a probabilistic basis, the imprecision of the proposed design is smaller than the other available schemes.

#### IV. MULTIPLICATION

In this section, the impact of using the proposed compressors for multiplication is investigated. A fast (exact) multiplier is usually composed of three parts (or *modules*) [8].

- Partial product generation.

- A Carry Save Adder (CSA) tree to reduce the partial products' matrix to an addition of only two operands

- A Carry Propagation Adder (CPA) for the final computation of the binary result.

In the design of a multiplier, the second module plays a pivotal role in terms of delay, power consumption and circuit complexity. Compressors have been widely used [9, 10] to speed up the CSA tree and decrease its power dissipation, so to achieve fast and low-power operation. The use of approximate compressors in the CSA tree of a multiplier results in an approximate multiplier.

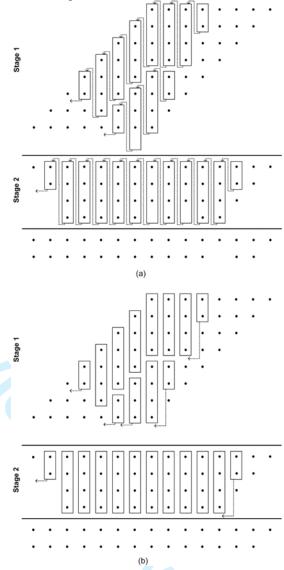

A  $8 \times 8$  unsigned Dadda tree multiplier is considered to assess the impact of using the proposed compressors in approximate multipliers. The proposed multiplier uses in the first part AND gates to generate all partial products. In the second part, the approximate compressors proposed in the previous section are utilized in the CSA tree to reduce the partial products. The last part is an exact CPA to compute the final binary result. Figure 9(a) shows the reduction circuitry of an exact multiplier for n=8. In this figure, the reduction part uses half-adders, full-adders and 4-2 compressors; each partial product bit is represented by a dot. In the first stage, 2 halfadders, 2 full-adders and 8 compressors are utilized to reduce the partial products into at most four rows. In the second or final stage, 1 half-adder, 1 full-adder and 10 compressors are used to compute the two final rows of partial products. Therefore, two stages of reduction and 3 half-adders, 3 full-adders and 18 compressors are needed in the reduction circuitry of an  $8 \times 8$ Dadda multiplier.

In this paper, four cases are considered for designing an approximate multiplier.

Figure 9. Reduction circuitry of an 8×8Dadda multiplier, (a) using Design 1 compressors, (b) using Design 2 compressors

- In the first case (Multiplier 1), Design 1 is used for all 4-2 compressors in Figure 9(a).

- In the second case (Multiplier 2), Design 2 is used for the 4-2 compressors. Since Design 2 does not have  $c_{in}$  and  $c_{out}$ , the reduction circuitry of this multiplier requires a lower number of compressors (Figure 9(b)). Multiplier 2 uses 6 half-adders, 1 full-adder and 17 compressors.

- In the third case (Multiplier 3), Design 1 is used for the compressors in the*n*-*1* least significant columns. The other *n* most significant columns in the reduction circuitry use exact 4-2 compressors.

6

• In the fourth case (Multiplier 4), Design 2 and exact 4-2 compressors are used in the*n*-1 least significant columns and the*n* most significant columns in the reduction circuitry respectively.

The objectives of the first two approximate designs are to reduce the delay and power consumption compared with an exact multiplier; however, a high error distance is expected. The next two approximate multipliers (i.e. Multipliers 3 and 4) are proposed to decrease the error distance. The delay in these designs is determined by the exact compressors that are in the critical path; therefore, there is no improvement in delay for these approximate designs compared with an exact multiplier. However, it is expected that the utilization of approximate compressors in the least significant columns will decrease the power consumption and transistor count (as measure of circuit complexity). While the first two proposed multipliers have better performance in terms of delay and power consumption, the error distances in the third and fourth designs are expected to be significantly lower.

## V. SIMULATION RESULTS

In this section, he designs of the two approximate compressors (Section III) and the four approximate multipliers (Section IV) are simulated using HSPICE. Predictive Technology Models (PTMs) at different CMOS feature sizes (32 nm, 22 nm and 16 nm) are utilized in the HSPICE simulation.

### A. Approximate Compressors

The two approximate compressors of this paper and the best low-power exact compressor of [8] (implemented by using *XOR-XNOR* gates) are simulated at a 1 GHz frequency; a fanout of 4 is utilized in all simulations. The simulation results of the delay, power consumption and power-delay product (PDP) are given in Table IV by using the PTMs at 32 nm, 22 nm and 16 nm.

TABLE IV SIMULATION RESULTS (@32 NM)

| Design           | Delay(ps) | $Power(\mu W)$ | PDP(aJ) |

|------------------|-----------|----------------|---------|

|                  | @32 nm    | !              |         |

| Exact Design [8] | 60.36     | 2.98           | 180     |

| Design 1         | 58.32     | 1.27           | 74      |

| Design 2         | 44.35     | 1.14           | 50      |

|                  | @22 nm    | !              |         |

| Exact Design [8] | 55.82     | 1.50           | 84      |

| Design 1         | 56.79     | 0.62           | 35      |

| Design 2         | 41.69     | 0.58           | 24      |

|                  | @16 nm    | !              |         |

| Exact Design [8] | 47.59     | 0.95           | 45      |

| Design 1         | 37.16     | 0.39           | 14      |

| Design 2         | 24.44     | 0.36           | 9       |

As expected, the second proposed design (Design 2) has the best delay, power consumption and PDP; these improvements are irrespective of feature size. This approximate design is 62% faster than the exact compressor at 16 nm CMOS technology and 44% faster on average for the three feature sizes considered. Moreover on average, Design 2 is also 35% faster than Design 1. The two proposed approximate designs

achieve significant improvement in terms of power consumption; on average at different feature sizes, the power consumption of Design 1 is 57% less than the exact compressor, while Design 2 has a power consumption that is 60% less than the exact design of [8].

Table V compares these designs in terms of number of transistors, as a measure of circuit complexity. The exact compressor [8] uses 10 transistors to implement each  $XOR^*$  gate, 6 transistors to implement the XOR gate and 8 transistors to implement each MUX gate [8]; therefore, the exact compressor utilizes 52 transistors. A 50% improvement in circuit complexity is accomplished by Design 2, as reflected by the lower number of transistors. This is expected because the second approximate design has no  $c_{in}$  and  $c_{out}$  with only 4 inputs and 2 outputs (the exact compressor has 5 inputs and 3 outputs).

| TA               | ABLE V                |

|------------------|-----------------------|

| COMPARISON OF N  | UMBER OF TRANSISTORS  |

| Design           | Number of transistors |

| Exact Design [8] | 52                    |

| Design 1         | 28                    |

| Design 2         | 26                    |

## B. Approximate Multipliers

The four proposed approximate multipliers are simulated for n=8. The delay, power consumption and number of transistors are investigated for these approximate designs as well as the exact multiplier. A comparison of the error distance (as measure of reliability [1]) of the proposed multipliers with other approximate multipliers is also pursued.

#### • Delay

The delay of the reduction circuitry (second module) of a Dadda multiplier is dependent on the number of reduction stages and the delay of each stage. In Multipliers 1 and 2, the approximate compressors are used in all columns; therefore, the delay of the stages is equal to the delay of the approximate compressors. However, in Multipliers 3 and 4, the delay of the stages is equal to the delay of the exact compressors. So, the use of these approximate compressors in the n/2 LSBs cause no improvement in terms of delay compared to an exact multiplier. The delay improvement in the reduction circuitry of each multiplier (at 32 nm CMOS technology) compared to an exact adder is shown in Table VI.

TABLE VI DELAY IMPROVEMENT IN REDUCTION CIRCUITRY

| Design       | Improvement (%) |

|--------------|-----------------|

| Multiplier 1 | 3.38            |

| Multiplier 2 | 26.52           |

| Multiplier 3 | 0               |

| Multiplier 4 | 0               |

• Power Consumption

-

The power consumption of each multiplier is determined by the number and type of compressors used. Multipliers 1 and 2 use only approximate compressors so they have power consumption lower than Multipliers 3 and 4. Table VII shows

1

the power consumption improvement of each multiplier at 32 nm feature size with respect to an exact adder; this confirms that an approximate multiplier in the reduction circuitry will result in a considerable power saving.

|                      | TABLE VII                        |

|----------------------|----------------------------------|

| POWER CONSUMPTION IM | PROVEMENT IN REDUCTION CIRCUITRY |

| Design               | Improvement (%)                  |

| Multiplier 1         | 52.49                            |

| Multiplier 2         | 58.58                            |

| Multiplier 3         | 17.50                            |

| Multiplier 4         | 26.15                            |

## • Transistor Count

The transistor count is used in this paper as metric of circuit complexity. The first two approximate multipliers have a lower transistor count compared with Multipliers 3 and 4. Table VIII shows the transistor count improvement of the reduction circuitry of each multiplier compared to an exact adder.

| -            | CABLE VIII<br>OVEMENT IN REDUCTION CIRCUITRY |

|--------------|----------------------------------------------|

| Design       | Improvement (%)                              |

| Multiplier 1 | 42.11                                        |

| Multiplier 2 | 48.15                                        |

| Multiplier 3 | 14.03                                        |

| Multiplier 4 | 22.42                                        |

## • Error Distance

Four additional approximate multipliers are simulated to compare the error distance. The multiplier (Multiplier 5) proposed in [7] is simulated for n=8. The truncated multiplier with constant correction [5] (Multiplier 6) and the truncated multiplier with variable correction [6] (Multiplier 7) are also simulated for n=8 and k=1. A further approximate multiplier (Multiplier 8) is simulated to investigate the impact of using the proposed approximate compressors compared with other approximate compressors. This  $8 \times 8$  Dadda multiplier uses 4-2 compressors made of two approximate full-adders (Figure 3). The first full-adder design proposed in [2] is used in this approximate multiplier. Table IX summarizes the eight approximate multipliers assessed in this manuscript, i.e. the four proposed designs and the other four approximate multipliers together with their salient features.

TABLE IX

| APPRU            | DAIMATE MULTIPLIERS AND THEIR FEATURES        |

|------------------|-----------------------------------------------|

| Design           | Feature                                       |

| Multiplier 1     | Design 1 in all columns                       |

| Multiplier 2     | Design 2 in all columns                       |

| Multiplier 3     | Design 1 in LSBs and exact compressor in MSBs |

| Multiplier 4     | Design 2 in LSBs and exact compressor in MSBs |

| Multiplier 5 [7] | Approximate 2x2 multiplier blocks             |

| Multiplier 6 [5] | Truncated multiplier with constant correction |

| Multiplier 7 [6] | Truncated multiplier with variable correction |

| Multiplier 8     | Compressors made of approximate FAs [2]       |

The normalized error distance (NED) is used to compare these approximate multipliers. In [1], the NED is defined as the average error distance over all inputs, normalized by the maximum possible error. In this paper the NED is defined for each input. Therefore the average NED is equivalent to the NED defined in [1]. The maximum high (low) NED is also defined as the largest absolute value of NED for the case in which the erroneous result is more (less) than the exact result. Table X shows the average NED, the maximum high and low NEDs and the number of correct results (or outputs) of approximate multipliers for n=8. The number of correct outputs out of the total outputs represents the probability of correctness for each design. Based on Table X, the probability of correctness in Multiplier 1 is 0.16% (103 out of 65025) while the probability of correctness in Multiplier 4 is 14.3% (9320 out of 65025). Since the proposed approximate compressors produce erroneous results for all-zero input patterns (row 1 in Tables II and III), the proposed approximate multipliers will generate an erroneous result if at least one of the inputs is zero. However, in these cases (511 cases for n=8) the multiplier can produce correct result by adding a circuit for detecting the zero-valued inputs. Therefore, the zero-valued input patterns are not considered further in the simulation to investigate the proposed multipliers for a fair comparison.

|    |                  |                         | TABLEX<br>NED FOR N = 8 |                         |                                   |

|----|------------------|-------------------------|-------------------------|-------------------------|-----------------------------------|

|    | Design           | Average<br>NED          | Max High<br>NED         | Max Low<br>NED          | correct outputs<br>(out of 65025) |

|    | Multiplier 1     | 0.6065×10 <sup>-1</sup> | 0.1593                  | 0.1375                  | 103                               |

|    | Multiplier 2     | 0.5352×10 <sup>-1</sup> | 0.1278                  | 0.1329                  | 458                               |

|    | Multiplier 3     | 0.9199×10 <sup>-3</sup> | 0.3199×10 <sup>-2</sup> | 0.2707×10 <sup>-2</sup> | 5888                              |

|    | Multiplier 4     | 0.7827×10 <sup>-3</sup> | 0.1845×10 <sup>-2</sup> | 0.3076×10 <sup>-2</sup> | 9320                              |

| D  | Multiplier 5 [7] | 0.1400×10 <sup>-1</sup> | 0                       | 0.2222                  | 34400                             |

| )  | Multiplier 6 [5] | 0.1609×10 <sup>-2</sup> | 0.3937×10 <sup>-2</sup> | 0.9858×10 <sup>-2</sup> | 0                                 |

| r  | Multiplier 7 [6] | 0.1146×10 <sup>-2</sup> | 0.3060×10 <sup>-2</sup> | 0.4045×10 <sup>-2</sup> | 769                               |

| 1_ | Multiplier 8     | 0.1049                  | 0.2263                  | 0.1207                  | 8                                 |

Based on Table X, Multiplier 4 has the lowest average NED among all approximate multipliers. The average NED of Multiplier 4 is 18 times better than Multiplier 5, 2 times better than Multiplier 6 and 1.5 times better than Multiplier 7. Multiplier 5 has the highest number of correct outputs. It has also the lowest maximum high NED. As the approximate output is always less than the exact output, the maximum high NED is 0 for this design; however, it has the worst maximum low NED among all considered designs.

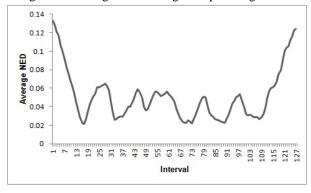

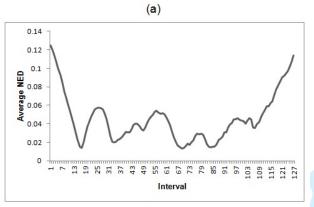

A plot of the NED distribution is also generated (Figure 10) to compare the performance of the approximate multipliers. The range of the product in a  $8 \times 8$  multiplier is between 0 and 65025 (unsigned values). All possible outputs are categorized in 127 intervals; in the first interval the output is between 0 and 512, in the second interval the output is between 513 and 1024 and so on. In the last interval the output is between 64513 and 65025. The average NED of each interval is then computed for the approximate multiplier. Figures 10a and 10b show that for Multipliers 1 and 2, the average NED increases only at very large or very small product values, i.e. these approximate multiplier incur on average in a small error in output compared to the exact calculation.

## VI. APPLICATION: IMAGE PROCESSING

In this section the application of the proposed approximate

multipliers to image processing is illustrated. A multiplier is used to multiply two images on a pixel by pixel basis, thus blending the two images into a single output image.

(d)

Figure10.Average NED distribution in  $8\times 8$  approximate multipliers. (a) Multiplier 1, (b) Multiplier 2, (c) Multiplier 3, (d) Multiplier 4

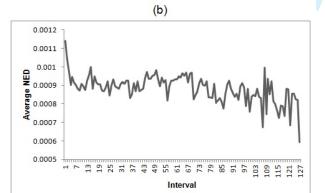

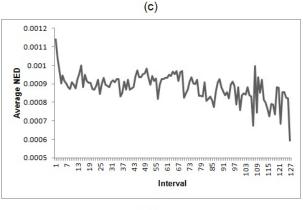

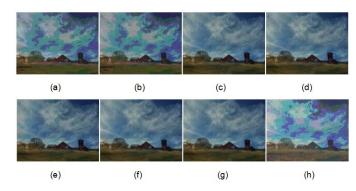

Figure 11 shows two examples: both input images and the resulting output image are provided. A program has been developed in C# .net and simulated in Microsoft Visual Studio 2010 using the 8 approximate multipliers at n=8. Figures 12 and 13 show the outputs for the two examples.

The average NED and the Peak Signal-to-Noise Ratio (PSNR) that is based on the Mean Squared Error (MSE) are computed to assess the quality of the output image and compare it with the output image generated by an exact multiplier. The equations for the MSE and PSNR are given in (10) and (11); in (10), *m* and *p* are the image dimensions and I(i,j) and K(i,j) are the exact and obtained values of each pixel respectively. In (11),  $MAX_I$  represents the maximum value of each pixel.

$$MSE = \frac{1}{mp} \sum_{i=0}^{m-1} \sum_{j=0}^{p-1} [I(i,j) - K(i,j)]^2$$

(10)

$$PSNR = 10 log_{10}(\frac{MAX_l^2}{MSE})$$

(11)

Figure 11. Image multiplication (a) example 1, (b) example 2 (both using an exact multiplier)

(a) (b) (c) (d)

(e) (f) (g) (h) Figure 12. Image multiplication results for example 1, (a) Multiplier 1, (b) Multiplier 2, (c) Multiplier 3, (d) Multiplier 4, (e) Multiplier 5, (f) Multiplier 6, (g) Multiplier 7, (h) Multiplier 8.

Figure 13. Image multiplication results for example2, (a) Multiplier 1, (b) Multiplier 2, (c) Multiplier 3, (d) Multiplier 4, (e) Multiplier 5, (f) Multiplier 6, (g) Multiplier 7, (h) Multiplier 8

| Design                                                                                                         | PSNR (dB)                                                                   | Average NED(×10 <sup>-2</sup> )                                                                     |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Multiplier 1                                                                                                   | 25.3                                                                        | 4.4                                                                                                 |

| Multiplier 2                                                                                                   | 26.3                                                                        | 3.7                                                                                                 |

| Multiplier 3                                                                                                   | 53.9                                                                        | 0.10                                                                                                |

| Multiplier 4                                                                                                   | 53.2                                                                        | 0.12                                                                                                |

| Multiplier 5 [7]                                                                                               | 26.3                                                                        | 2.3                                                                                                 |

| Multiplier 6 [5]                                                                                               | 48.3                                                                        | 0.28                                                                                                |

| Multiplier 7 [6]                                                                                               | 52.3                                                                        | 0.15                                                                                                |

| Multiplier 8                                                                                                   | 21.2                                                                        | 7.6                                                                                                 |

| DOND                                                                                                           | TABLE XII                                                                   | -                                                                                                   |

|                                                                                                                | VERAGE NED FOR                                                              | SECOND EXAMPLE                                                                                      |

| Design                                                                                                         | VERAGE NED FOR<br>PSNR (dB)                                                 | A SECOND EXAMPLE Average NED(×10 <sup>-2</sup> )                                                    |

| <i>Design</i><br>Multiplier 1                                                                                  | VERAGE NED FOR<br>PSNR (dB)<br>25.1                                         | A SECOND EXAMPLE<br>Average NED(×10 <sup>-2</sup> )<br>4.5                                          |

| <i>Design</i><br>Multiplier 1<br>Multiplier 2                                                                  | VERAGE NED FOR<br><i>PSNR (dB)</i><br>25.1<br>25.8                          | R SECOND EXAMPLE<br>Average NED(×10 <sup>-2</sup> )<br>4.5<br>4.1                                   |

| Design<br>Multiplier 1<br>Multiplier 2<br>Multiplier 3                                                         | VERAGE NED FOR<br>PSNR (dB)<br>25.1<br>25.8<br>54.2                         | <u>R SECOND EXAMPLE</u><br><u>Average NED(×10<sup>-2</sup>)</u><br>4.5<br>4.1<br>0.096              |

| Design<br>Multiplier 1<br>Multiplier 2<br>Multiplier 3<br>Multiplier 4                                         | VERAGE NED FOR<br>PSNR (dB)<br>25.1<br>25.8<br>54.2<br>54.9                 | <u>R SECOND EXAMPLE</u><br><u>Average NED(×10<sup>-2</sup>)</u><br>4.5<br>4.1<br>0.096<br>0.083     |

| Design<br>Multiplier 1<br>Multiplier 2<br>Multiplier 3<br>Multiplier 4<br>Multiplier 5 [7]                     | VERAGE NED FOR<br>PSNR (dB)<br>25.1<br>25.8<br>54.2<br>54.9<br>35.7         | R SECOND EXAMPLE<br>Average NED(×10 <sup>-2</sup> )<br>4.5<br>4.1<br>0.096<br>0.083<br>0.72         |

| Design<br>Multiplier 1<br>Multiplier 2<br>Multiplier 3<br>Multiplier 4<br>Multiplier 5 [7]<br>Multiplier 6 [5] | VERAGE NED FOR<br>PSNR (dB)<br>25.1<br>25.8<br>54.2<br>54.9<br>35.7<br>52.4 | R SECOND EXAMPLE<br>Average NED(×10 <sup>-2</sup> )<br>4.5<br>4.1<br>0.096<br>0.083<br>0.72<br>0.14 |

| Design<br>Multiplier 1<br>Multiplier 2<br>Multiplier 3<br>Multiplier 4<br>Multiplier 5 [7]                     | VERAGE NED FOR<br>PSNR (dB)<br>25.1<br>25.8<br>54.2<br>54.9<br>35.7         | R SECOND EXAMPLE<br>Average NED(×10 <sup>-2</sup> )<br>4.5<br>4.1<br>0.096<br>0.083<br>0.72         |

Tables XI and XII show that the PSNRs of the output images generated by Multipliers 3 and 4, are nearly 50 dB, a value that is acceptable for most applications. Consistently, Multiplier 1 has the worst PSNR among 4 proposed designs. As discussed previously, the proposed approximate multipliers have a higher error distance for very large and very small input values in the product operands. Therefore the pixels that have high RGB (Red-Green-Blue) model values (such as of a white color) or small RGB model values (such as those of a black color), show a larger inaccuracy than other pixels due to the approximate nature of the compressors. However, the error distance of Multipliers3 and 4 still remains very low.

## VII. CONCLUSION

Inexact computing is an emerging paradigm for computation at nanoscale. Computer arithmetic offers significant operational advantages for inexact computing; an extensive literature exists on approximate adders. However, this paper has initially focused on compression as used in a multiplier; to the best knowledge of the authors, no work has been reported on this topic.

This paper has presented the novel designs of two approximate 4-2 compressors. These approximate

compressors are utilized in the reduction module of four approximate multipliers. The approximate compressors show a significant reduction in transistor count, power consumption and delay compared with an exact design.

9

- In terms of transistor count, the first design has a 46% improvement, while the second design has a 50% improvement.

- In terms of power consumption, the first design has a 57% improvement and the second design has a 60% improvement on average for CMOS implementation at feature sizes of 32, 22 and 16 nm.

- In terms of delay, the second design has a 44% improvement compared to the exact compressor and 35% improvement compared to the first design on average at different CMOS feature sizes of 32, 22 and 16 nm.

Four different approximate schemes have been proposed in this paper to investigate the performance of the approximate compressors for the aforementioned metrics for inexact multiplication. The approximate compressors have been utilized in the reduction module of a Dadda multiplier. The following conclusions can be drawn from the simulation results presented in this manuscript.

- The first and second proposed multipliers show a significant improvement in terms of power consumption and transistor count compared to an exact multiplier.

- The first and second multipliers have larger average NEDs (and thus, larger PSNRs), while the second multiplier that uses the second proposed approximate compressor for all bits, has the best delay.

- With relatively modest reductions in transistor count and power consumption, the third and fourth proposed multipliers have very low average NED values, thus presenting the best tradeoff for energy with accuracy.

Moreover, the application of these approximate multipliers to image processing has confirmed that two of the proposed designs achieve a PSNR of nearly 50dB in the output generated by multiplying two input images, thus viable for most applications.

Table XIII compares the four proposed approximate design with four other approximate designs found in the technical literature by ranking them under various metrics. Multiplier 4 is overall the best design with respect to all figures of merit for approximate multiplication as well as the two PSNR examples. Multiplier 5 has the best performance in terms of Max High NED and number of correct outputs; however, its rather poor performance for the other figures of merit causes its ranking to be in the middle once the PSNR examples are considered. Multiplier 3 is the second best design among the schemes considered in this manuscript. It offers overall good performance in most metrics of Table XIII. Current and future research addresses the tradeoffs of the different figures of merit in the proposed designs to establish conditions by which combined metrics can be attained. Moreover, physical designs of the approximate multipliers are being pursued to further confirm the analysis presented in this paper.

In conclusion, this paper has shown that by an appropriate design of an approximate compressor, multipliers can be designed for inexact computing; these multipliers offer significant advantages in terms of both circuit-level and error

## **Transactions on Computers**

Page 10 of 13

figures of merit. Although not discussed and beyond the scope of this manuscript, the proposed designs may also be useful in other arithmetic circuits for applications in which inexact computing can be used. The provision of an error indicator (as required for other applications) is a topic of current investigation.

| TABLE XIII                      |

|---------------------------------|

| DANKING OF ADDROVIMATE MULTIDUE |

| RANKING OF APPROXIMATE MULTIPLIERS |             |              |             |                 |                |                |

|------------------------------------|-------------|--------------|-------------|-----------------|----------------|----------------|

| Design                             | Average NED | Max High NED | Max Low NED | Correct Outputs | PSNR example 1 | PSNR example 2 |

| Multiplier 1                       | 7           | 7            | 7           | 6               | 7              | 7              |

| Multiplier 2                       | 6           | 6            | 6           | 5               | 5              | 6              |

| Multiplier 3                       | 2           | 4            | 1           | 3               | 1              | 2              |

| Multiplier 4                       | 1           | 2            | 2           | 2               | 2              | 1              |

| Multiplier 5 [7]                   | 5           | 1            | 8           | 1               | 5              | 5              |

| Multiplier 6 [5]                   | 4           | 5            | 4           | 8               | 4              | 4              |

| Multiplier 7 [6]                   | 3           | 3            | 3           | 4               | 3              | 3              |

| Multiplier 8                       | 8           | 8            | 5           | 7               | 8              | 8              |

#### REFERENCES

- J. Liang, J. Han, F. Lombardi, "New Metrics for the Reliability of Approximate and Probabilistic Adders," *IEEE Transactions on Computers*, vol. 63, no. 9, pp. 1760 - 1771, 2013.

- [2] V. Gupta, D. Mohapatra, S. P. Park, A. Raghunathan, K. Roy, "IMPACT: IMPrecise adders for low-power approximate computing," *Low Power Electronics and Design (ISLPED)* 2011 International Symposium on. 1-3 Aug. 2011.

- [3] S. Cheemalavagu, P. Korkmaz, K.V. Palem, B.E.S. Akgul, and L.N. Chakrapani, "A probabilistic CMOS switch and its realization by exploiting noise," in *Proc. IFIP-VLSI SoC*, Perth, Western Australia, Oct. 2005.

- [4] H.R. Mahdiani, A. Ahmadi, S.M. Fakhraie, C. Lucas, "Bio-Inspired Imprecise Computational Blocks for Efficient VLSI Implementation of Soft-Computing Applications," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57, no. 4, pp. 850-862, April 2010.

- [5] M. J. Schulte and E. E. Swartzlander, Jr., "Truncated multiplication with correction constant," VLSI Signal Processing VI, pp. 388–396, 1993.

- [6] E. J. King and E. E. Swartzlander, Jr., "Data dependent truncated scheme for parallel multiplication," in *Proceedings of the Thirty First Asilomar Conference on Signals, Circuits and Systems*, pp. 1178–1182, 1998.

- [7] P. Kulkarni, P. Gupta, and MD Ercegovac, "Trading accuracy for power in a multiplier architecture", Journal of Low Power Electronics, vol. 7, no. 4, pp. 490--501, 2011.

- [8] C. Chang, J. Gu, M. Zhang, "Ultra Low-Voltage Low- Power CMOS 4-2 and 5-2 Compressors for Fast Arithmetic Circuits," *IEEE Transactions* on Circuits & Systems, Vol. 51, No. 10, pp. 1985-1997, Oct. 2004.

- [9] D. Radhakrishnan and A. P. Preethy, "Low-power CMOS pass logic 4-2 compressor for high-speed multiplication," in *Proc. 43rd IEEE Midwest Symp. Circuits Syst.*, vol. 3, 2000, pp. 1296–1298.

- [10] Z. Wang, G. A. Jullien, and W. C. Miller, "A new design technique for column compression multipliers," *IEEE Trans. Comput.*, vol. 44, pp. 962–970, Aug. 1995.

- [11] J. Gu, C. H. Chang, "Ultra Low-voltage, low-power 4-2 compressor for high speed multiplications," in *Proc. 36th IEEE Int. Symp. Circuits Systems*, Bangkok, Thailand, May 2003.

- [12] M. Margala and N. G. Durdle, "Low-power low-voltage 4-2 compressors for VLSI applications," in *Proc. IEEE Alessandro Volta Memorial Workshop Low-Power Design*, 1999, pp. 84–90.

- [13] B. Parhami, "Computer Arithmetic: Algorithms and Hardware Designs," 2nd edition, Oxford University Press, New York, 2010.

- [14] K. Prasad and K. K. Parhi, "Low-power 4-2 and 5-2 compressors," in Proc. of the 35th Asilomar Conf. on Signals, Systems and Computers, vol. 1, 2001, pp. 129–133.

- [15] Ercegovac, Miloš D., and Tomas Lang. Digital arithmetic. Elsevier, 2003.

- [16] Baran, Dursun, Mustafa Aktan, and Vojin G. Oklobdzija. "Energy efficient implementation of parallel CMOS multipliers with improved compressors." *Proc. of the 16th ACM/IEEE international symposium on Low power electronics and design*. ACM, 2010.

- [17] D. Kelly, B. Phillips, S. Al-Sarawi, "Approximate signed binary integer multipliers for arithmetic data value speculation", in Proc. of the conference on design and architectures for signal and image processing, 2009.

- [18] J. Ma, K. Man, T. Krilavicius, S. Guan, and T. Jeong, "Implementation of High Performance Multipliers Based on Approximate Compressor Design" in international Conference on Electrical and Control Technologies (ECT), 2011.

Fabrizio Lombardi (M'81–SM'02-F'09) graduated in 1977 from the University of Essex (UK) with a B.Sc. (Hons.) in Electronic Engineering. In 1977 he joined the Microwave Research Unit at University College London, where he received the Master in Microwaves and Modern Optics (1978), the Diploma in Microwave Engineering (1978) and the Ph.D. from the University of London (1982).He is currently the holder of the International Test

Conference (ITC) Endowed Chair Professorship at Northeastern University, Boston. During 2007-2010 Dr. Lombardi was the Editor-In-Chief of the IEEE Transactions on Computers. He is also an Associate Editor of the IEEE Transactions on Nanotechnology and the inaugural Editor-in-Chief of the IEEE Transactions on Emerging Topics in Computing. He currently serves as an elected Member of the Board of Governors of the IEEE Computer Society. His research interests are bioinspired and nano manufacturing/computing, VLSI design, testing, and fault/defect tolerance of digital systems. He has extensively published in these areas and coauthored/edited seven books.

**Jie Han** (S'02–M'05) received the B.Sc. degree in electronic engineering from Tsinghua University, Beijing, China, in 1999 and the Ph.D. degree from Delft University of Technology, The Netherlands, in 2004. He is currently an assistant professor in the Department of Electrical and Computer Engineering at the University of Alberta, Edmonton, AB, Canada. His research interests include reliability and fault tolerance, nanoelectronic circuits and systems, novel computational models for

nanoscale and biological applications.Dr. Han was nominated for the 2006 Christiaan Huygens Prize of Science by the Royal Dutch Academy of Science (KoninklijkeNederlandseAkademie van Wetenschappen (KNAW) Christiaan Huygens Wetenschapsprijs). His work was recognized by the 125th anniversary issue of *Science*, for developing theory of fault-tolerant nanocircuits. He served as a Technical Program Chair and a General Chair in IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT) 2012 and 2013, respectively. He has also served as a Technical Program Committee Member in several other international symposia and conferences.

58

59

60

Paolo Montuschi is a Professor of Computer Engineering at Politecnico di Torino and Deputy Chair of the Control and Computer Engineering Department. Previously, he served as Chair of Department from 2003 to 2011, and as Chair or Member of several Boards. He is currently serving as Associate Editor-in-Chief of the IEEE Transactions on Computers, as well as member of the

steering committee of the IEEE Transactions on Emerging Topics in Computing and of the Advisory Board of Computing Now. He is also serving in the Board of Governors of the IEEE Computer Society, as Chair of the Magazine Operations Committee of the Computer Society and member of the Publications Board, Audit and Digital Library Operations Committees. Previously, he served as chair of the Electronic Products and Services and the Digital Library Operations Committees, member of Electronic Products and Services Committee, Member-at-Large of the Computer Society's Publications Board, and Member of Conference Publications Operations Committee. He served as guest and associate editor of the IEEE Transactions on Computers from 2000 to 2004 and from 2009 to 2012, and co-chair, program and steering committee member of several conferences. His current main research interests and scientific achievements are in computer arithmetic, architectures, graphics, and new publication frameworks for "augmented reading" and scientific knowledge dissemination. Within the Computer Society he is actively involved in opening the door to new publication frameworks geared towards e-reading and mobile devices. He is a Computer Society Golden Core Member, and an IEEE Senior Member. Montuschi obtained a PhD in computer engineering in 1989, and since 2000 he has been full Professor.

Amir Momeni received the BS degree in computer engineering from Sharif University of Technology, and the MS degree in computer engineering from Shahid Beheshti University, Iran. He is currently working toward the PhD degree in computer engineering at Northeastern University. His research interests include VLSI, EDA, parallel computing, and heterogeneous systems. He is a student member of the IEEE.