# Preface

### About This Manual

This manual provides a general overview of designing Field Programmable Gate Arrays (FPGAs) with HDLs. It also includes design hints for the novice HDL user and for the experienced user who is designing FPGAs for the first time.

The design examples in this manual were created with the VHSIC Hardware Description Language (VHDL); compiled with the Synopsys FPGA Compiler; and targeted for XC4000 devices. However, most of the design methodologies also apply to Verilog, other synthesis tools, and other Xilinx FPGAs. Xilinx equally endorses both Verilog and VHDL. VHDL may be more difficult to learn than Verilog and usually requires more explanation. You can download the VHDL design examples and the Verilog versions of many of the designs either from the Xilinx Internet Site or the Xilinx Technical Bulletin Board.

Before using this manual, you should be familiar with the operations that are common to all Xilinx's software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. These topics are covered in the *Development System Reference Guide*.

Refer to the *Synopsys (XSI)—FPGAs Interface/Tutorial Guide* and the *Synopsys (XSI)—EPLDs Interface/Tutorial Guide* for information on implementing XC3000, XC3100, and XC7000 devices and for more information on implementing XC4000 device features.

Other publications you can consult for related information are the *X-BLOX Reference/User Guide, Floorplanner Reference/User Guide, Libraries Guide,* and the *High-Density Design Guide* application note.

This manual does not address certain topics that are important when creating HDL designs, such as the design environment, verification techniques, constraining in the synthesis tool, test considerations, and system verification. If you use Synopsys tools, refer to the Synopsys reference manuals, design methodology notes, and SOLV-IT for additional information.

### How to Use This Manual

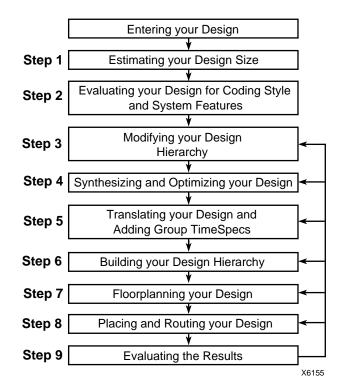

Chapter 6, "Understanding High-Density Design Flow", describes the steps in the high-density design flow and includes information from the five previous chapters in the manual. You may want to review Chapter 6 first to get an overview of the design flow and then refer to the appropriate chapters for detailed information on a specific step in the flow.

### **Manual Contents**

This manual covers the following topics.

- Chapter 1, "Getting Started," provides a general overview of designing Field Programmable Gate Arrays (FPGAs) with HDLs. This chapter also includes installation requirements and instructions.

- Chapter 2, "HDL Coding Hints," discusses HDL coding hints and design examples to help you develop an efficient coding style.

- Chapter 3, "HDL Coding for FPGAs," provides design examples to help you incorporate FPGA system features into your HDL designs.

- Chapter 4, "Floorplanning Your Design," describes basic operation of the Xilinx Floorplanner and provides HDL design examples that facilitate floorplanning.

- Chapter 5, "Building Design Hierarchy," describes how to partition your designs to improve synthesis results and reduce routing congestion.

- Chapter 6, "Understanding High-Density Design Flow," discusses the design flow for high-density HDL designs.

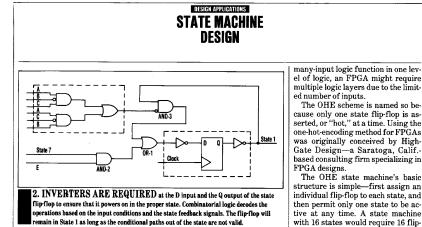

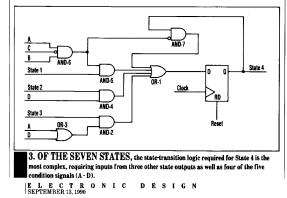

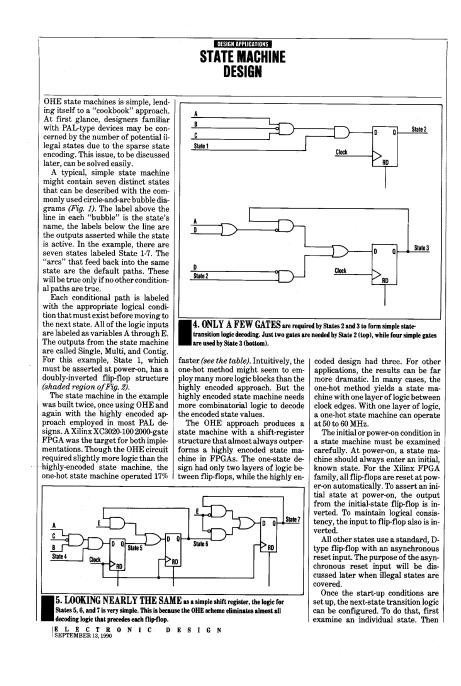

- Appendix A, "Accelerate FPGA Macros with One-Hot Approach," reprints an article describing one-hot encoding in detail.

- Appendix B, "Top Design Scripts," includes the three script files used to compile the Top design described in the "Building Design Hierarchy" chapter of this manual.

- Appendix C, "Tactical Software and Design Examples," lists the tactical software and design examples that are described in this manual.

# Conventions

| The following conven statements. | tions are used in this manual's syntactical                                           |

|----------------------------------|---------------------------------------------------------------------------------------|

| Courier font<br>regular          | System messages or program files appear in regular Courier font.                      |

| Courier font<br>bold             | Literal commands that you must enter in syntax statements are in bold Courier font.   |

| italic font                      | Variables that you replace in syntax statements are in italic font.                   |

| []                               | Square brackets denote optional items or parameters.                                  |

| { }                              | Braces enclose a list of items from which you must choose one or more.                |

|                                  | A vertical ellipsis indicates material that has been omitted.                         |

|                                  | A horizontal ellipsis indicates that the preceding can be repeated one or more times. |

|                                  | A vertical bar separates items in a list of choices.                                  |

| <b>ب</b>                         | This symbol denotes a carriage return.                                                |

HDL Synthesis for FPGAs — 0401294 01

# Chapter 1 Getting Started

| Understanding HDL Design Flow for FPGAs                 | 1-1  |

|---------------------------------------------------------|------|

| Entering Your Design                                    |      |

| Verifying Your Design                                   |      |

| Floorplanning Your Design                               |      |

| Placing and Routing Your Design                         |      |

| Advantages of Using HDLs to Design FPGAs                |      |

| Designing FPGAs with HDLs                               |      |

| Using VHDL.                                             |      |

| Comparing ASICs and FPGAs                               |      |

| Using Synthesis Tools                                   |      |

| Using FPGA System Features                              |      |

| Designing Hierarchy                                     |      |

| Specifying Speed Requirements                           |      |

| Installing Design Examples and Tactical Software        |      |

| Software Requirements                                   |      |

| SPARC and HP-PA Requirements                            |      |

| Disk Space Requirements                                 |      |

| Xilinx Internet Site                                    |      |

| Xilinx Technical Bulletin Board                         | 1-9  |

| Retrieving Tactical Software and Design Examples        | 1-9  |

| From Xilinx Internet FTP Site                           |      |

| From Xilinx Technical Bulletin Board                    |      |

| Extracting the Files                                    | 1-11 |

| Directory Tree Structure                                | 1-12 |

| Synopsys Startup File and Library Setup                 |      |

| Technical Support                                       | 1-14 |

| Important Issues                                        | 1-14 |

| 0 0 0                                                   | 1-15 |

| Block Names are Not Written by Default in Synopsys FPGA |      |

| Compiler V3.3b                                          | 1-16 |

| Creating MAP Files                                      | 1-16 |

# Chapter 2 HDL Coding Hints

| Comparing Synthesis and Simulation Results | 2-2 |

|--------------------------------------------|-----|

| Omit the Wait for XX ns Statement          |     |

| Omit theAfter XX ns Statement              | 2-2 |

| Use Case and If-Else Statements            | 2-2 |

| Order and Group Arithmetic Functions       | 2-3 |

| Omit Initial Values                        | 2-3 |

| Selecting VHDL Coding Styles                    | 2-3  |

|-------------------------------------------------|------|

| Selecting a Capitalization Style                | 2-4  |

| Using Xilinx Naming Conventions                 | 2-4  |

| Naming Identifiers, Types, and Packages         | 2-5  |

| Using Labels                                    | 2-5  |

| Using Variables for Constants                   | 2-6  |

| Using Named and Positional Association          | 2-6  |

| Managing Your Design                            | 2-7  |

| Creating Readable Code                          | 2-7  |

| Indenting Your Code                             | 2-7  |

| Using Empty Lines                               | 2-7  |

| Using Spaces                                    |      |

| Breaking Long Lines of Code                     | 2-8  |

| Adding Comments                                 | 2-8  |

| Using Std_logic Data Type                       |      |

| Declaring Ports                                 |      |

| Minimizing the Use of Ports Declared as Buffers |      |

| Comparing Signals and Variables                 | 2-10 |

| Using Schematic Design Hints with HDL Designs   |      |

| Barrel Shifter Design                           |      |

| Implementing Latches and Registers              | 2-16 |

| Resource Sharing                                | 2-20 |

| Gate Reduction                                  |      |

| Preset Pin or Clear Pin                         | 2-27 |

| Using Clock Enable Pin                          | 2-30 |

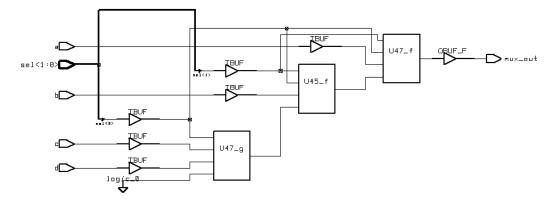

| Using If Statements                             | 2-31 |

| Using Case Statements                           | 2-32 |

| Using Nested_If Statements                      |      |

| Comparing If Statement and Case Statement       | 2-37 |

|                                                 |      |

# Chapter 3 HDL Coding for FPGAs

| Using Global Low-skew Clock Buffers           | 3-2 |

|-----------------------------------------------|-----|

| Inserting Clock Buffers                       | 3-4 |

| Instantiating Internal Global Clock Buffers   | 3-4 |

| Using Dedicated Global Set/Reset Resource     | 3-4 |

| Startup State                                 | 3-5 |

| Preset vs. Clear                              | 3-5 |

| Increasing Performance with the GSR Net       | 3-6 |

| Design Example without Dedicated GSR Resource | 3-6 |

| Design Example with Dedicated GSR Resource    | 3-8 |

Xilinx Development System

| Design Example with Dedicated GSR Resource and  |      |

|-------------------------------------------------|------|

| Additional Preset Signal                        | 3-11 |

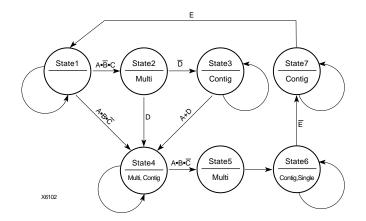

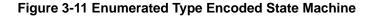

| Encoding State Machines                         | 3-13 |

| Using Binary Encoding                           | 3-14 |

| Using Enumerated Type Encoding                  |      |

| Using One-Hot Encoding                          | 3-17 |

| Summary of Encoding Styles                      |      |

| Comparing Synthesis Results for Encoding Styles |      |

| Initializing the State Machine                  | 3-20 |

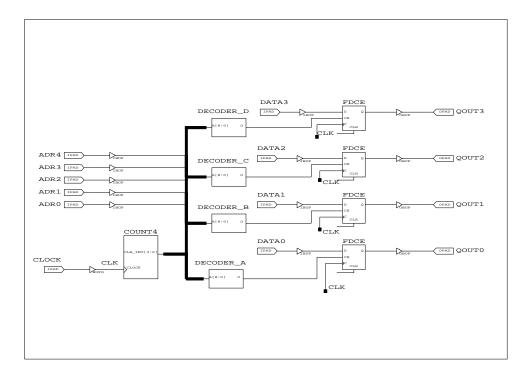

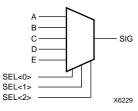

| Using Dedicated I/O Decoders                    |      |

| Instantiating X-BLOX Modules                    | 3-25 |

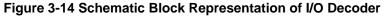

| Using X-BLOXGen                                 | 3-26 |

| Syntax                                          | 3-27 |

| Options                                         | 3-28 |

| Output Files                                    | 3-28 |

| X-BLOXGen Example                               | 3-28 |

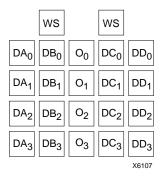

| Using RPMs                                      | 3-32 |

| Instantiating an RPM                            | 3-34 |

| Implementing Memory                             | 3-36 |

| Implementing XC4000 RAMs                        |      |

| Implementing XC4000 ROMs                        | 3-36 |

| Using MemGen                                    | 3-38 |

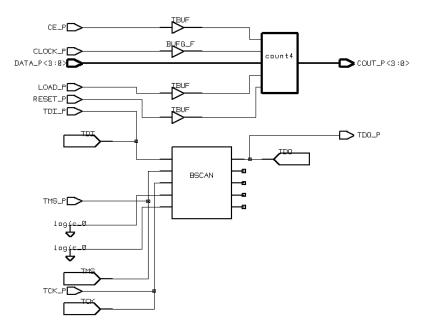

| Implementing Boundary Scan (JTAG 1149.1)        |      |

| Instantiating the Boundary Scan Symbol          | 3-40 |

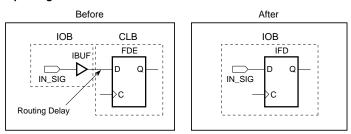

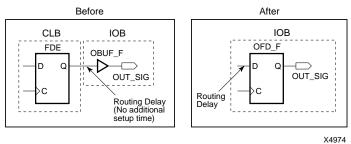

| Implementing Logic with IOBs                    |      |

| XC4000/A/D IOBs                                 |      |

| Inputs                                          | 3-43 |

| Outputs                                         | 3-43 |

| XC4000/D Slew Rate                              | 3-43 |

| XC4000A Slew Rate                               |      |

| XC4000H IOBs                                    |      |

| Inputs                                          |      |

| Outputs                                         |      |

| XC4000H Slew Rate                               |      |

| Instantiating Bidirectional I/O                 |      |

| Moving Registers into the IOB                   |      |

| Using Unbonded IOBs (XC4000/A/D Only)           |      |

| Implementing Multiplexers with Tristate Buffers |      |

| Setting Timing Constraints                      |      |

| Using the Synthesis Tool                        |      |

| Using PPR Command Line Options                  | 3-54 |

HDL Synthesis for FPGAs

| Using A Constraints File                          | 3-55 |

|---------------------------------------------------|------|

| Using TIMESPEC and TIMEGRP Commands               | 3-55 |

| Using TIMESPEC and TIMEGRP Constraints File       |      |

| Statements                                        | 3-56 |

| Using MakeTNM and AddTNM                          | 3-57 |

| Adding TNMs                                       | 3-57 |

| Creating A TNM Control File Without Using MakeTNM | 3-65 |

| Adding TNMs to Signals                            | 3-66 |

|                                                   |      |

### Chapter 4 Floorplanning Your Design

| Using the Floorplanner                          | 4-2  |

|-------------------------------------------------|------|

| Creating a MAP File                             | 4-2  |

| Using XMake                                     | 4-2  |

| Using PPR                                       |      |

| Using Prep for Floorplanner Command             | 4-2  |

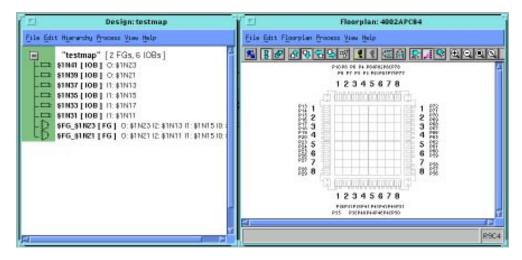

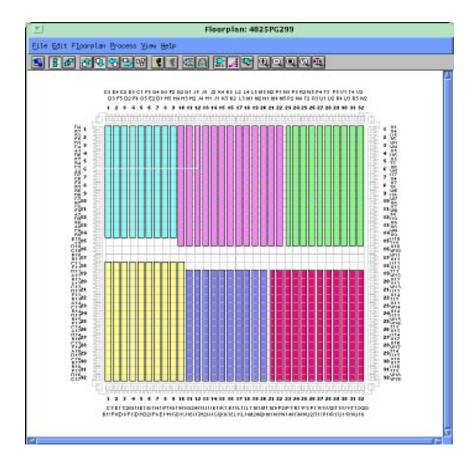

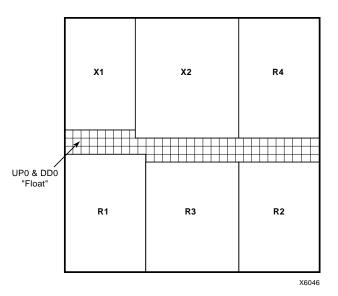

| Overview of Floorplanner Windows                | 4-3  |

| Task Window                                     | 4-3  |

| Design Window                                   | 4-3  |

| Floorplan Window                                |      |

| Deciding What Elements to Floorplan             |      |

| Running the Floorplanner and Opening a File     | 4-6  |

| Using the Command Line                          | 4-6  |

| Using the Floorplanner Task Window              | 4-6  |

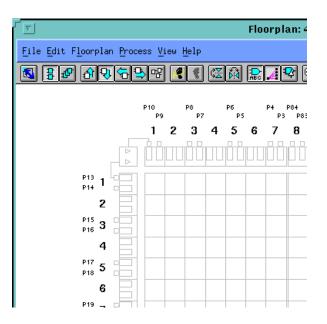

| Setting Boundaries in the Floorplan Window      |      |

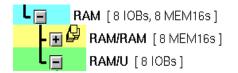

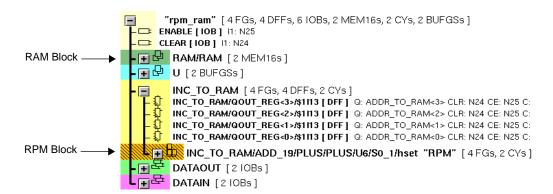

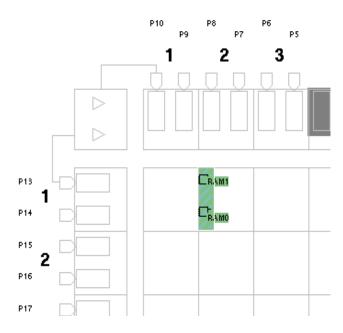

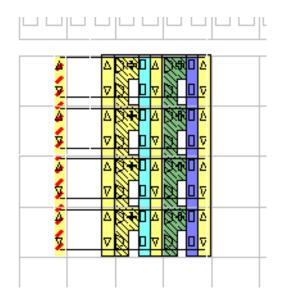

| Floorplanning RPMs, RAMs, and ROMs              |      |

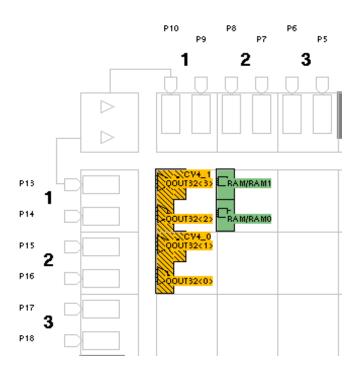

| RPM and RAM/ROM Example                         |      |

| Floorplanning Tristate Buffers                  | 4-13 |

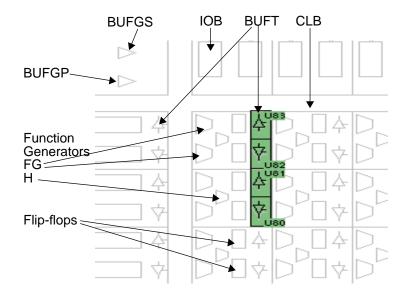

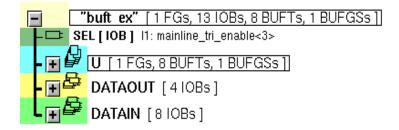

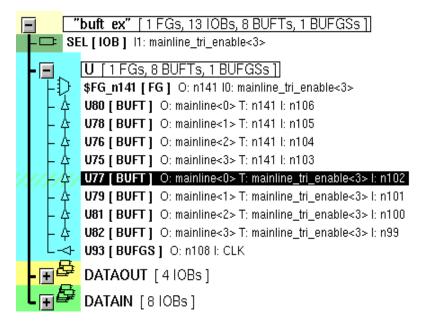

| BUFT Example                                    |      |

| Floorplanning BUFT Example                      |      |

| Comparing Hierarchical and Flat Designs         |      |

| Method 1: Compiling Flat without X-BLOX         |      |

| Method 2: Compiling Flat with X-BLOX            | 4-26 |

| Method 3: Compiling with Hierarchy and without  |      |

| X-BLOX                                          |      |

| Method 4: Compiling with Hierarchy and X-BLOX   |      |

| Floorplanning to Reduce Routing Congestion      |      |

| Positioning and Aligning Buses                  |      |

| Aligning Structures Along Buses                 |      |

| Floorplanning RAMs to Reduce Routing Congestion | 4-34 |

|                                                 |      |

| Chapter 5 | Building Design meralicity                                         |      |

|-----------|--------------------------------------------------------------------|------|

|           | Using the Synthesis Tool                                           | 5-2  |

|           | Modifying Design Hierarchy for PPR                                 | 5-3  |

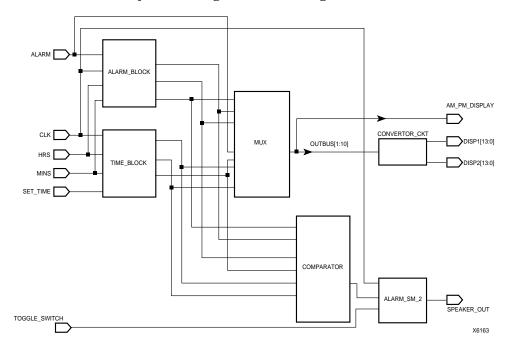

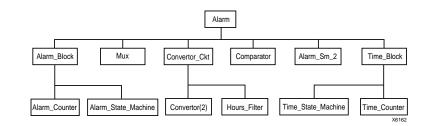

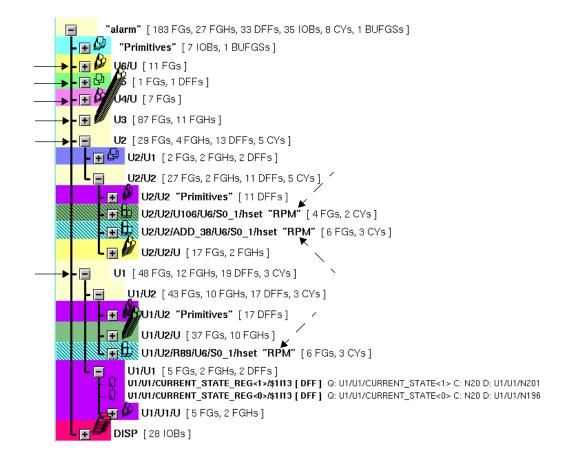

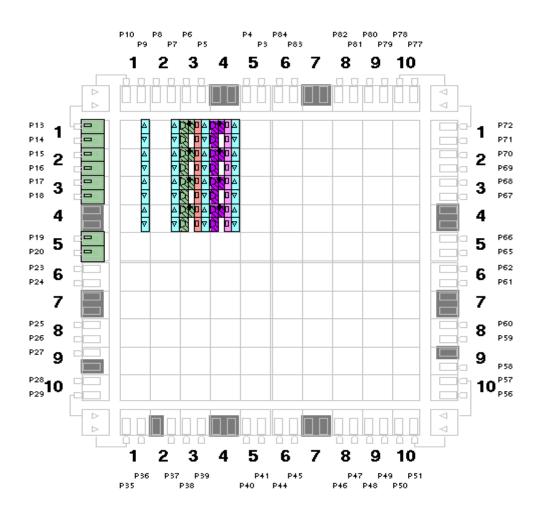

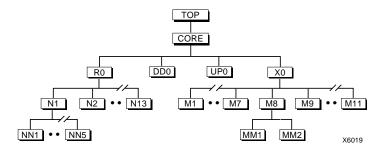

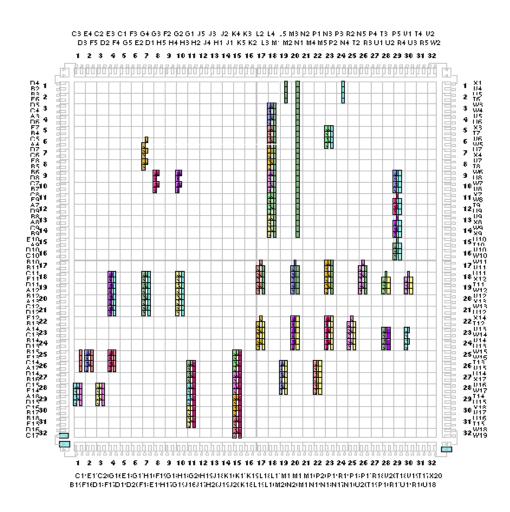

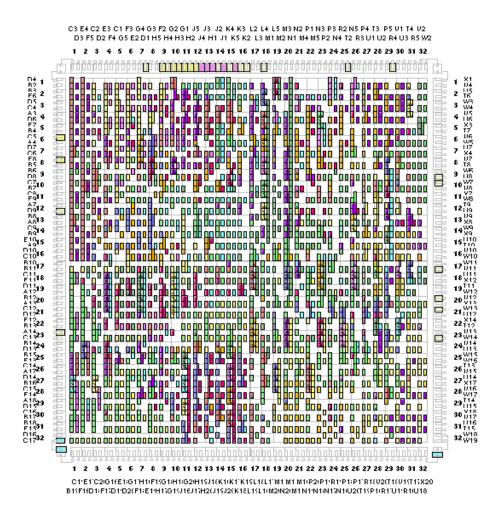

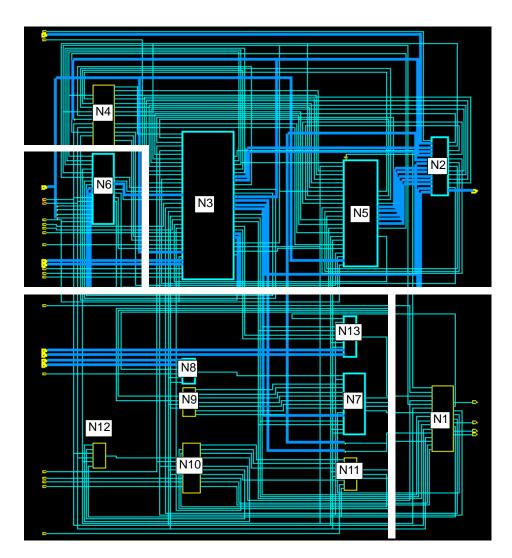

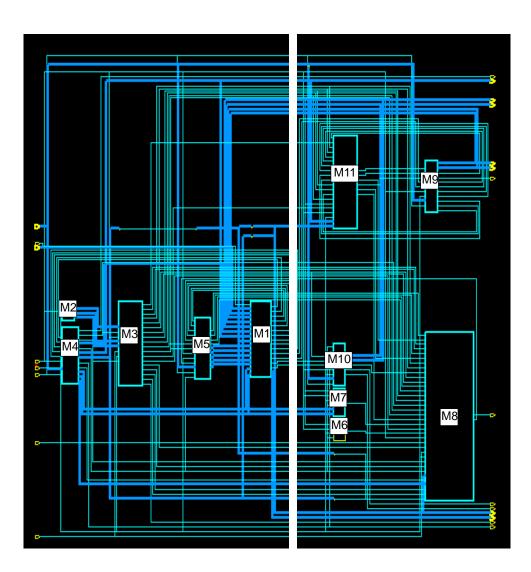

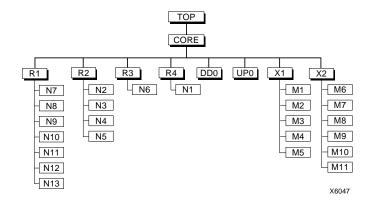

|           | Top Design Example                                                 | 5-4  |

|           | Compiling Top Design as One Flat Module                            | 5-7  |

|           | Compiling Top Design Using Original Hierarchy                      | 5-8  |

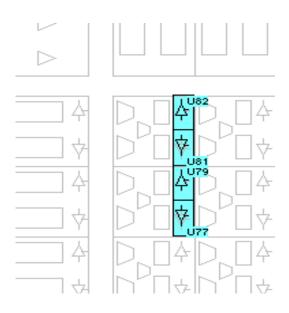

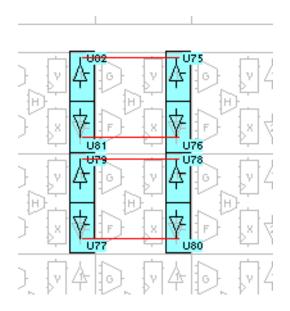

|           | Floorplanning RPMs                                                 | 5-8  |

|           | Meeting Speed Requirements                                         |      |

|           | Compiling Top Design After Modifying the Hierarchy                 |      |

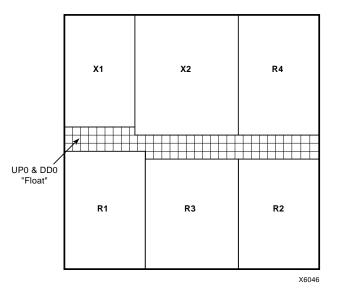

|           | Evaluating A New Hierarchy                                         |      |

|           | Defining and Compiling the New Hierarchy                           |      |

|           | Setting Boundaries and Floorplanning the Modules                   |      |

|           | Floorplanning Structured Cells                                     |      |

|           | Placing and Routing the Top Design                                 |      |

|           | Adding Probe Points to Debug a Design                              |      |

|           | Comparing Top Design Methodologies                                 |      |

|           | Flat Design                                                        |      |

|           | Original Design Hierarchy                                          |      |

|           | Modified Hierarchy                                                 | 5-24 |

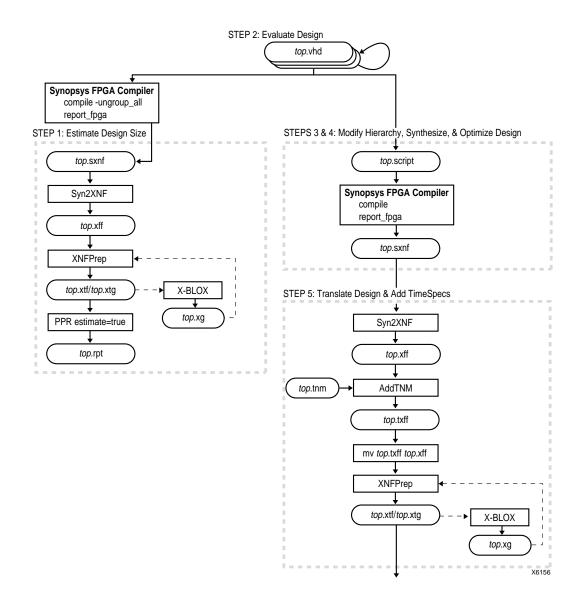

| Chapter 6 | Understanding High-Density Design Flow                             |      |

|           | Step 1: Estimating Your Design Size                                | 6-4  |

|           | Determining Device Utilization                                     | 6-5  |

|           | Step 2: Evaluating Your Design for Coding Style and System         |      |

|           | Features                                                           |      |

|           | Step 3: Modifying Your Design Hierarchy                            |      |

|           | Estimating Area Utilization                                        |      |

|           | Creating a New Hierarchy                                           |      |

|           | Step 4: Synthesizing and Optimizing Your Design                    |      |

|           | Step 5: Translating Your Design and Adding Group TimeSpecs.        |      |

|           | Translating Your Design                                            |      |

|           | Adding Timing Specifications                                       |      |

|           | Using the Synthesis Tool                                           |      |

|           | Using PPR Command Line Options                                     |      |

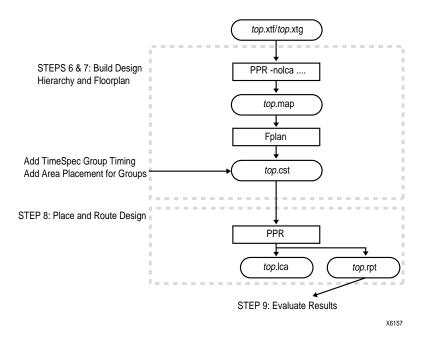

|           | Using A Constraints File<br>Step 6: Building Your Design Hierarchy |      |

|           | Step 6. Building Your Design Hierarchy                             |      |

|           | Creating a MAP File                                                |      |

|           | Using XMake                                                        |      |

|           | Using PPR                                                          |      |

|           | eeing i i it                                                       | 5 10 |

### Chapter 5 Building Design Hierarchy

HDL Synthesis for FPGAs

| Using Prep for Floorplanner Option                | 6-16 |

|---------------------------------------------------|------|

| Floorplanning Design Components                   | 6-16 |

| Writing a Constraints File                        | 6-17 |

| Step 8: Placing and Routing Your Design           | 6-17 |

| Using PPR Options                                 | 6-18 |

| Determining If PPR Can Route Your Design          | 6-19 |

| Step 9: Evaluating the Results                    | 6-19 |

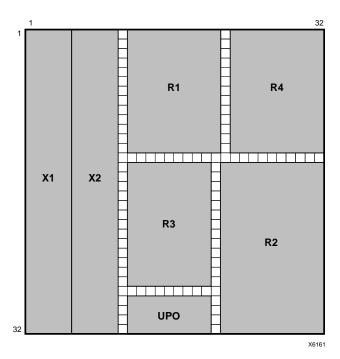

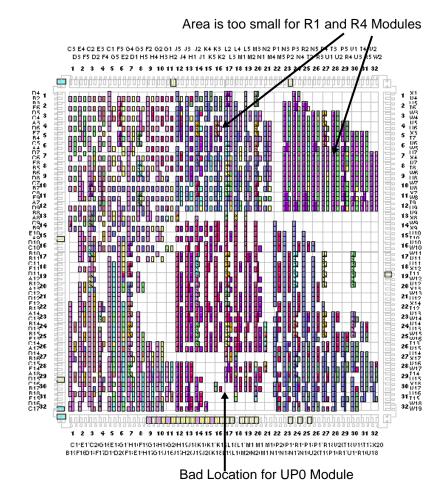

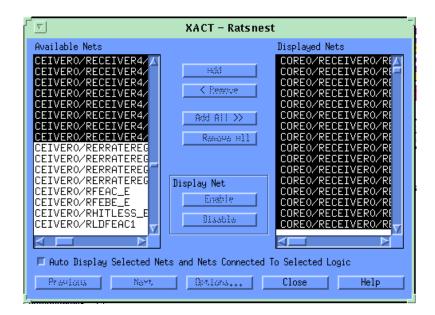

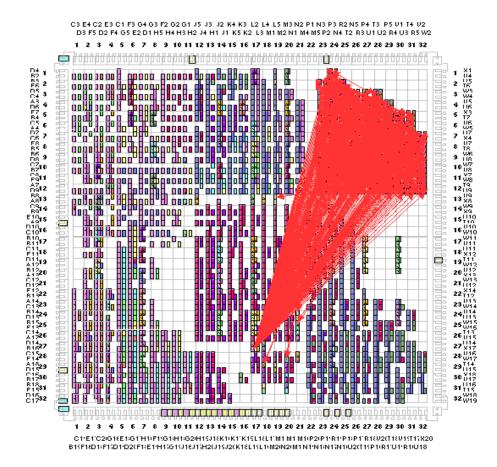

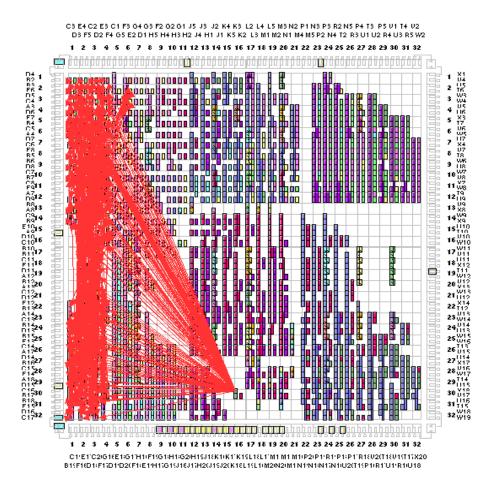

| Evaluating Module Placement with the Floorplanner | 6-20 |

| Modifying Design Placement                        | 6-25 |

| Using Guided Design                               | 6-26 |

| Using Iterative Guided Design                     | 6-27 |

| Using Incremental Guided Design                   |      |

| Using XDE                                         | 6-27 |

| Effectively Using Guided Design                   |      |

| Understanding Guided Design for XC4000 Designs    | 6-28 |

| Adding a New Module to Your Design                | 6-28 |

| Making a Design Change to a Module                | 6-29 |

|                                                   |      |

### Appendix A Accelerate FPGA Macros with One-Hot Approach

### Appendix B Top Design Scripts

| VHDL Script Files    | B-1 |

|----------------------|-----|

| Verilog Script Files | B-6 |

### Appendix C Tactical Software and Design Examples

| Tactical Software | C-1 |

|-------------------|-----|

| Design Examples   | C-2 |

# **Chapter 1**

# **Getting Started**

Hardware Description Languages (HDLs) are used to describe the behavior and structure of system and circuit designs. This chapter provides a general overview of designing FPGAs with HDLs. It also includes design hints for the novice HDL user and for the experienced user who is designing FPGAs for the first time. System requirements and installation instructions are also provided.

To learn more about designing FPGAs with HDLs, Xilinx recommends that you enroll in the appropriate training classes offered by Xilinx and by the vendors of synthesis software. Understanding FPGA architecture allows you to create HDL code that effectively uses FPGA system features.

# **Understanding HDL Design Flow for FPGAs**

Application Specific Integrated Circuit (ASIC) designs or sections of these designs that are targeted for FPGAs are often created with HDLs. However, the design flow for processing ASIC HDL code is slightly different from the flow used to process HDL code written specifically for FPGAs.

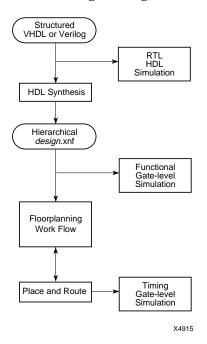

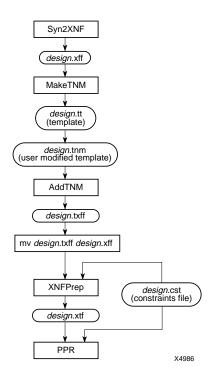

Figure 1-1 shows the design flow for an FPGA design. This design flow includes the following steps.

- 1. Creating your FPGA design with an HDL.

- 2. Performing a Register Transfer Level (RTL) simulation of your design.

- 3. Synthesizing your design.

- 4. Creating a Xilinx Netlist File (XNF) file.

- 5. Performing a functional simulation of your design.

- 6. Floorplanning your design. This step is optional.

- 7. Placing and routing (implementing) your design.

- 8. Performing a timing simulation of your design.

Figure 1-1 HDL Flow Diagram for a New Design

The design flow for ASICs differs depending on the quality of the existing code. You must analyze the ASIC design to determine if the code meets speed and area requirements for FPGAs. Additionally, you should structure the design hierarchy for FPGA implementation.

# **Entering Your Design**

When coding in HDL, you should create efficient code that utilizes FPGA system features and is structured into hierarchical blocks. These topics are described in detail in this manual.

### Verifying Your Design

You can behaviorally simulate your HDL designs to test system and device functionality before synthesis. After simulation, your design is synthesized and optimized for the target device. The hierarchical HDL code is then written as XNF files. After placement and routing, the design is simulated with the actual gate and wire delays.

Xilinx recommends that you perform an RTL or functional simulation of your design before floorplanning the cells (CLBs, IOBs, BUFTs) into the FPGA. If you find functional errors during a simulation performed after floorplanning, you must correct your code, resynthesize your design, and repeat the floorplanning process. The Xilinx Floorplanner builds a constraints file that includes the cell names in your design. If the cell names change, as they might if you resynthesize your design, the names in the constraints file are no longer correct.

### **Floorplanning Your Design**

Floorplanning is an optional step in the design flow. You can improve device density and increase the speed of critical paths by floorplanning parts or all of your design with the Xilinx Floorplanner. You can generate a constraints file that is read by PPR. Refer to the "Floorplanning Your Design" chapter in this manual for more information on floorplanning.

### **Placing and Routing Your Design**

After floorplanning, run PPR to place and route your design. PPR reads the constraints file generated by the Floorplanner and places logic that is not floorplanned. After your design is placed and routed, perform a timing simulation. You can back-annotate timing information to the Synopsys timing analysis tool.

# Advantages of Using HDLs to Design FPGAs

Using HDLs to design high-density FPGAs is advantageous for the following reasons.

• Top-Down Approach for Large Projects

HDLs are used to create complex designs. The top-down

approach to system design supported by HDLs is advantageous for large projects that require many designers working together. Once the overall design plan is determined, designers can work independently on separate sections of the code.

• Functional Simulation Early in the Design Flow

You can verify the functionality of your design early in the design flow by simulating the HDL description. Testing your design decisions before the design is implemented at the gate level allows you to make any necessary changes early in the design process.

Automatic Conversion of HDL Code to Gates

You can automatically convert your hardware description to a design implemented with gates. This step decreases design time by eliminating the traditional gate-level bottleneck. This automatic conversion to gates also reduces the number of errors that may be introduced during a manual translation of a hardware description to a schematic design. Additionally, you can apply the techniques used by the synthesis tool during the optimization of your design to the original HDL code, resulting in greater efficiency.

• Type Checking

HDLs provide type checking. For example, you cannot connect a 3- or 5-bit wide signal to a component that requires a 4-bit wide signal type. Additionally, if the range of a bus is 1 to 15, you cannot assign the bus a value of 0. Using incorrect types is a major source of errors in HDL descriptions. Type checking eliminates these errors in the description before a design is generated.

• Early Testing of Various Design Implementations

HDLs allow you to test different implementations of your design early in the design flow. You can then use the synthesis tool to perform the logic synthesis and optimization into gates. Additionally, Xilinx FPGAs allow you to implement your design at your computer. Since the synthesis time is short, you have more time to explore different architectural possibilities at the Register Transfer Level (RTL). You can reprogram Xilinx FPGAs to test several implementations of your design.

# **Designing FPGAs with HDLs**

If you are more familiar with schematic design entry, you may find it difficult at first to create HDL designs. You must make the transition from graphical concepts, such as block diagrams, state machines, flow diagrams and truth tables, to abstract representations of design components. You can ease this transition by not losing sight of your overall design plan as you code in HDL. To effectively use an HDL, you must understand the language syntax, the synthesis tool, the architecture of the target device, and the implementation tools. This section gives you some design hints to help you create FPGAs with HDLs.

### Using VHDL

VHSIC Hardware Description Language (VHDL) is a hardware description language for designing Integrated Circuits (ICs). It was not originally intended as an input to synthesis, and many VHDL constructs are not supported by synthesis software. In addition, the various synthesis tools use different subsets of the VHDL language. The examples provided in this manual are written in VHDL. The coding strategies presented in the remaining chapters of this manual can help you create HDL descriptions that can be synthesized.

### Comparing ASICs and FPGAs

Methods used to design ASICs do not always apply to FPGA designs. ASICs have more gate and routing resources than FPGAs. Since ASICs have a large number of available resources, you can easily create inefficient code that results in a large number of gates. When designing FPGAs, you *must* create efficient code.

### **Using Synthesis Tools**

Synthesis tools, such as the Synopsys FPGA Compiler, have special optimization algorithms for Xilinx FPGAs. Constraints and compiling options perform differently depending on the target device. There are some commands and constraints that do not apply to FPGAs and, if used, may adversely impact your results. You should understand how your synthesis tool processes designs before creating FPGA designs.

### **Using FPGA System Features**

You can improve device performance and area utilization by creating HDL code that uses FPGA system features, such as global reset, wide I/O decoders, and memory. FPGA system features are described in this manual.

### **Designing Hierarchy**

Current HDL design methods are specifically written for ASIC designs. You can use some of these ASIC design methods when designing FPGAs, however, certain techniques can greatly increase the number of gates.

Design hierarchy is important in the implementation of an FPGA and also during incremental or interactive changes. You should partition large designs (greater than 5,000 gates) into modules. The size and content of the modules influence synthesis results and design implementation. How to create effective design hierarchy is described in this manual.

### Specifying Speed Requirements

To meet timing requirements, you should understand how to set timing constraints in both the synthesis and placement/routing tools. You should also know how to manually place critical paths and structured modules with the Xilinx Floorplanner. See the *Floorplanner Reference/User Guide* for more information.

# Installing Design Examples and Tactical Software

The information in this section supplements the information in the Xilinx Synopsys Interface Version 3.3 Release Document. Read and follow the instructions in the Release Documents for Xilinx Synopsys Interface V3.3 or V5.1.

Three tactical software programs are required for the HDL examples in this manual. The three programs are X-BLOXGen, MakeTNM, and AddTNM. These programs are not included in the Xilinx Synopsys Interface or the XACT*step* Development System.

AddTNM and MakeTNM were created with Perl 4.0. To run these programs, you must have either Perl 4.0 or 5.0.

This manual includes numerous HDL design examples. These designs were created with VHDL, however, Xilinx equally endorses both Verilog and VHDL. VHDL may be more difficult to learn than Verilog and usually requires more explanation. You can obtain Verilog versions of many of the design examples either from the Xilinx Internet Site or the Xilinx Technical Bulletin Board, as described below.

**Note:** See "Appendix C" for a complete listing of tactical software and design examples.

### **Software Requirements**

To synthesize, simulate, floorplan, and implement the design examples in this manual, you should have the following versions of software installed on your system.

| Software                              | Version                                                            |

|---------------------------------------|--------------------------------------------------------------------|

| Xilinx Synopsys Interface (XSI)       | 3.2.0 or later                                                     |

| XACTstep                              | 5.1.0 or later                                                     |

| XACT <i>step</i> Foundry <sup>*</sup> | 7.0 or later                                                       |

| Synopsys FPGA Compiler                | 3.2 or later                                                       |

| Xilinx Floorplanner                   | Contact Xilinx sales representa-<br>tive for copy of Floorplanner. |

| XC4025 die files                      | Contact Xilinx sales representa-<br>tive.                          |

#### Table 1-1 Software Versions

\* XACT*step* Foundry v7 does not support the Xilinx Floorplanner.

**Note:** The design examples in this manual were compiled with Synopsys V3.3a and XACT*step* V5.2.0 (pre-release), however, all programs, scripts, and design examples are compatible with the versions in Table 1-1.

### **SPARC and HP-PA Requirements**

The system requirements for the SPARC and HP-PA are identical to those described in Xilinx Synopsys Interface Release Document V3.3 or V5.1. Refer to this release documentation for more information.

### **Disk Space Requirements**

Before you install the programs and files, verify that your system meets the requirements listed in the tables below for the various options. The disk space requirements listed are an approximation and may not exactly match the actual numbers.

#### **Xilinx Internet Site**

To download the programs and files from the Xilinx Internet Site, you need to meet the disk requirements listed in Table 1-2.

| Directory        | Description                                                                                        | Compressed<br>File | Directory<br>Size |

|------------------|----------------------------------------------------------------------------------------------------|--------------------|-------------------|

| XSI_files        | <ul> <li>Tactical Code</li> <li>XNF files for RPMs</li> <li>Default Synopsys setup file</li> </ul> | 83 K               | 344 K             |

| XSI_vhdl         | VHDL Examples <i>with</i> SIM,<br>SYN and MRA files in Work<br>directory                           | 5.1 MB             | 13 MB             |

| XSI_vhdl_no_work | VHDL Examples <i>without</i><br>SIM, SYN and MRA files in<br>Work directory                        | 3.3 MB             | 10.2 MB           |

| XSI_verilog      | Verilog Examples                                                                                   | 3 MB               | 9.2 MB            |

#### Table 1-2 Internet Files

The XSI\_files directory contains tactical software, XNF files for RPMs, and a default XC4000 FPGA Compiler setup file.

The XSI\_vhdl\_no\_work directory is smaller than the XSI\_vhdl directory because it does not contain the contents of the Work directory. The Work directory contains the analyzed files, SYN, MRA, and SIM for each VHDL design file. You can create these files by analyzing the VHDL design files or by running the design script files. Copy one of these directories only; it is not necessary to copy both. If you want to decrease the download time, copy the XSI\_VHDL\_no\_work directory.

#### **Xilinx Technical Bulletin Board**

To download the programs and files from the Xilinx Technical Bulletin Board (XTBB), you need to meet the disk space requirements listed in Table 1-3. Due to file size restrictions on the XTBB, the VHDL and Verilog directories listed in Table 1-3 do not contain the entire set of files that are available via the Internet. However, you can generate the complete set of files by running the design scripts and invoking the Xilinx tools.

| Directory   | Description                                                                                                                                        | Compressed<br>File | Directory<br>Size |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|

| tactical.uu | <ul> <li>Tactical Code</li> <li>XNF files for RPMs</li> <li>Default Synopsys setup file</li> </ul>                                                 | 115 K              | 344 K             |

| vhdl_ex.uu  | design.vhd, design.log, design.rpt,<br>design.prp, design.lca, design.timing,<br>design.fpga, design.sxnf, design.db,<br>design.map, design.script | 2.6 MB             | 5.1 MB            |

| ver_ex.uu   | design.v, design.log, design.rpt,<br>design.prp, design.lca, design.timing,<br>design.fpga, design.sxnf, design.db,<br>design.map, design.script   | 2.5 MB             | 4.7 MB            |

#### Table 1-3 XTBB Files

### **Retrieving Tactical Software and Design Examples**

You can retrieve the tactical software and the HDL design examples from the Xilinx Internet Site or the XTBB. If you need assistance

retrieving the files, use the information listed in the "Technical Support" section of this chapter to contact the Xilinx Hotline.

You must install the retrieved files on the same system as XSI DS-401 and the Synopsys tools. Do not install the files into the XSI DS-401 or XACT*step* DS-502 directories since the files may be overwritten when the next version of XSI or XACT*step* software is installed.

#### From Xilinx Internet FTP Site

You can retrieve the programs and files from the Xilinx Internet FTP (File Transfer Protocol) Site. To access the Xilinx Internet FTP Site, you must have FTP available on your machine. For UNIX users, FTP is a UNIX utility. You can obtain the PC version of the FTP utility through third-party vendors.

To use FTP, your machine must be connected to the Internet and you must have permission to use FTP on remote sites. If you need more information on this procedure, contact your system administrator.

To retrieve the programs and files from the Xilinx Internet FTP Site, use the following procedure:

1. Go to the directory on your local machine where you want to download the files:

cd directory

2. Invoke the FTP utility:

UNIX users, type: ftp PC users: contact your system administrator for assistance

3. Connect to the Xilinx Internet machine, www.xilinx.com:

ftp> open xilinx.www.com

4. Log into a guest account. This account gives you download privileges.

Name (machine:user-name) : ftp

Guest login ok, send your complete e-mail address

as the password.

Password: your\_email\_address

5. Go to the pub/XSI\_HDL directory:

ftp> cd pub/XSI\_HDL

6. Retrieve the appropriate design files as follows:

ftp> get design\_files.tar.Z

7. Extract the files as described in the "Extracting the Files" section below.

#### From Xilinx Technical Bulletin Board

The Xilinx Technical Bulletin Board (XTBB) is a 24-hour electronic bulletin board available to all registered XACT*step* customers. XTBB includes application notes, utility programs, bug fixes, and updated data files such as package and speed files. If you have full XTBB privileges, you can read and retrieve files on the bulletin board, including the design examples in this manual. You can also upload files and leave messages for Xilinx personnel or other XTBB users. Refer to the 1994 version of *The Xilinx Programmable Logic Data Book* for a complete description of the XTBB, including how to locate and download files.

To retrieve the programs and files from the XTBB:

1. Go to the directory on your local machine where you want to download the files:

cd directory

- 2. Access the XTBB.

- 3. Locate the files in the application area of the XTBB. The directory names are listed in Table 1-3.

- 4. Retrieve the uuencoded files.

- 5. Extract the files as described below.

#### **Extracting the Files**

You must install the retrieved files on the same system as XSI DS-401 and the Synopsys tools. However, do not install the files into the XSI DS-401 or XACT*step* DS-502 directories since the files may be overwritten when the next version of XSI or XACT*step* software is installed.

To extract the files, use the following procedure.

Note: The first step only applies to files retrieved from the XTBB.

1. Undecode the files:

uudecode design.uu

2. Uncompress the files:

uncompress design.tar.Z

3. Extract the files:

tar xvf design.tar

4. Copy the tactical programs, AddTNM, MakeTNM, and X-BLOXGen, into a directory in your search path or into your working directory.

### **Directory Tree Structure**

After you have completed the installation, you should have the following directory tree structure and files:

```

XSI_files/

xbloxgen

addtnm

maketnm

fc4k.synopsys_db.setup

rpm_xnf/

acc16/

acc4/

acc8/

add16/

add4/

add8/

adsu16/

adsu4/

adsu8/

cc16ce/

cc16cle/

cc16cled/

ccl6re/

cc8ce/

cc8cle/

cc8cled/

cc8re/

compc16/

compmc8/

```

Xilinx Development System

XSI\_verilog/ alarm/ align\_str/ barrel/ bidi\_reg/ bnd\_scan/ bufts/ clock\_enable/ clr\_pre/ d\_latch/ d\_register/ ff\_example/ gate\_clock/ gate\_reduce/ gsr/ io\_decoder/ mux\_vs\_3state/ res\_sharing/ roml6x4/ rom\_memgen/ rpm\_example/ rpm\_ram/ state\_machine/ top\_hier/ unbonded\_io/ xbloxgen\_ex/ XSI\_vhdl/ or XSI\_vhdl\_no\_wk/ alarm/ align\_str/ barrel/ bidi\_reg/ bnd\_scan/ bufts/ case\_vs\_if/ clock\_enable/ clr\_pre/ d\_latch/ d\_register/ ff\_example/ gate\_clock/ gate\_reduce/ gsr/ io\_decoder/ mux\_vs\_3state/ nested\_if/ res\_sharing/ roml6x4/ rom\_memgen/ rpm\_example/

HDL Synthesis for FPGAs

rpm\_ram/

sig\_vs\_var/

state\_machine/

unbonded\_io/

xbloxgen\_ex/

# Synopsys Startup File and Library Setup

Follow the procedures in the "Getting Started" chapter of the *Synopsys (XSI)—FPGAs Interface/Tutorial Guide* for instructions on setting up the Synopsys start-up file for XC4000 designs using the Synopsys FPGA Compiler.

# **Technical Support**

This manual and associated files come with free technical and product information telephone support (toll-free in the U.S. and Canada). You can also fax or email your questions to Xilinx.

| • | United States and Canada                              |                    |

|---|-------------------------------------------------------|--------------------|

|   | Technical Support Hotline                             | 1-800-255-7778     |

|   | Technical Support FAX (24 hours/7 days)               | 1-408-879-4442     |

|   | Technical Support Bulletin Board<br>(24 hours/7 days) | 1-408-559-9327     |

|   | Internet E-mail Address (24 hours/7 days)             | hotline@xilinx.com |

| • | International                                         |                    |

|   | Technical Support Hotline                             | 1-408-879-5199     |

|   | Technical Support FAX (24 hours/7 days)               | 1-408-879-4442     |

|   | Technical Support Bulletin Board<br>(24 hours/7 days) | 1-408-559-9327     |

|   | Internet E-mail Address (24 hours/7 days)             | hotline@xilinx.com |

|   |                                                       |                    |

### **Important Issues**

This section includes important issues that are not covered in the remaining chapters of this manual.

### Instantiating XNF Files in Verilog Designs

To instantiate a module that is not in one of the target libraries, such as an XNF file created using MemGen or X-BLOXGen, you must create an additional module-endmodule statement for the XNF file in your Verilog code. The XNF file for the module must exist in the working directory (or in the search path for XNFMerge).

For example, use the following procedure to instantiate the acc4.xnf file in the rpm\_example.v design. Acc4.xnf was created with X-BLOXGen.

1. Create an additional module-endmodule statement for acc4.xnf in rpm\_example.v as follows:

module rpm\_example(B\_IN3, B\_IN2, B\_IN1, B\_IN0, D\_IN3, D\_IN2, D\_IN1, D\_IN0, CI\_IN, L\_IN, ADD\_IN, CE\_OUT, CLK\_IN, Q\_OUT3, Q\_OUT2, Q\_OUT1, Q\_OUT0, CO\_OUT, OFL\_OUT); input B\_IN3, B\_IN2, B\_IN1, B\_IN0, D\_IN3, D\_IN2, D\_IN1, D\_IN0, CI\_IN, L\_IN, ADD\_IN, CE\_OUT, CLK\_IN; output Q\_OUT3, Q\_OUT2, Q\_OUT1, Q\_OUT0, CO\_OUT, OFL\_OUT; acc4 U1 (.B3(B\_IN3), .B2(B\_IN2), .B1(B\_IN1), .B0(B\_IN0), .D3(D\_IN3), .D2(D\_IN2), .D1(D\_IN1), .D0(D\_IN0), .CI(CI\_IN), .L(L\_IN), .ADD(ADD\_IN), .CE(CE\_OUT), .C(CLK\_IN), .Q3(Q\_OUT3), .Q2(Q\_OUT2), .Q1(Q\_OUT1), .Q0(Q\_OUT0), .CO(CO\_OUT), .OFL(OFL\_OUT)); endmodule module acc4 (B3, B2, B1, B0, D3, D2, D1, D0, CI, L, ADD, CE, C, Q3, Q2, Q1, Q0, CO, OFL); input B3, B2, B1, B0, D3, D2, D1, D0, CI, L, ADD, CE, C; output Q3, Q2, Q1, Q0, CO, OFL;

endmodule

2. In your Synopsys script file, immediately before you write the SXNF file, enter this command:

#### remove\_design acc4

3. Run XMake on the top level file:

xmake rpm\_example

# Block Names are Not Written by Default in Synopsys FPGA Compiler V3.3b

In Synopsys FPGA Compiler V3.3b, block names for CLBs mapped with registers are not written to the SXNF file by default. If your script file contains the following statement, you can remove it.

```

set_attribute find(design, "*") "xnfout_use_blknames" \

-type boolean FALSE

```

The design examples in this manual do not contain this statement in the example script file. However, the example scripts in the Xilinx Synopsys Interface V3.2 and V3.3 include this statement. If you are using Synopsys V3.2 or earlier, you should set this attribute to FALSE and include the statement in your script file. If you are using Synopsys V3.3b or later, you can remove this statement because the attribute version is set to FALSE by default.

### **Creating MAP Files**

Do not use the outfile= option when creating a MAP file.

Xilinx Development System

# **Chapter 2**

# **HDL Coding Hints**

HDLs contain many complex constructs that can be difficult to understand at first. Additionally, the methods and examples included in HDL manuals do not always apply to designing FPGAs. If you currently use HDLs to design ASICs, your established coding style may increase the number of gates in FPGA designs. ASICs have more gates and routing resources than FPGAs, therefore, a design that fits an ASIC device may be unroutable in an FPGA.

HDL synthesis tools implement logic based on the coding style of your design. To learn how to efficiently code with HDLs, you can attend training classes, read reference and methodology notes, and refer to synthesis guidelines and templates available from Xilinx and the synthesis vendors. When coding your designs, remember that HDLs are mainly hardware description languages. You should try to find a balance between the quality of the end hardware results and the speed of simulation.

The coding hints and examples included in this chapter are not intended to teach you every aspect of VHDL, but they should help you develop an efficient coding style.

The following topics are included in this chapter:

- Comparing Synthesis and Simulation Results

- Selecting VHDL Coding Styles

- Using Schematic Design Hints with HDL Designs

# **Comparing Synthesis and Simulation Results**

VHDL is a hardware description and simulation language and was not originally intended as an input to synthesis. Therefore, many hardware description and simulation constructs are not supported by synthesis tools. In addition, the various synthesis tools use different subsets of the VHDL language. VHDL semantics are well defined for design simulation. The synthesis tools must adhere to these semantics to ensure that designs simulate the same way before and after synthesis. Follow the guidelines presented below to create code that simulates the same way before and after synthesis.

### **Omit the Wait for XX ns Statement**

Do not use the Wait for XX ns statement in your code. XX specifies the number of nanoseconds that must pass before a condition is executed. This statement does not synthesize to a component. In designs that include this statement, the functionality of the simulated design does not match the functionality of the synthesized design.

### Omit the ... After XX ns Statement

Do not use the ...After XX ns statement in your code. An example of this statement is:

(Q <=0 after XX ns)

XX specifies the number of nanoseconds that must pass before a condition is executed. This statement is usually ignored by the synthesis tool. In this case, the functionality of the simulated design does not match the functionality of the synthesized design.

#### **Use Case and If-Else Statements**

You can use either If-Else statements or Case statements to create state machines. Synthesis tools that support both types of statements implement the functions differently, however, the simulated designs are identical. The If-Else statement specifies priority-encoded logic and the Case statement specifies parallel behavior. The If-Else statement can result in a slower circuit overall. Refer to the "Comparing If Statement and Case Statement" section of this chapter for more information.

### **Order and Group Arithmetic Functions**

The ordering and grouping of arithmetic functions influences design performance. For example, the following two statements are not equivalent:

ADD <= A1 + A2 + A3 + A4;ADD <= (A1 + A2) + (A3 + A4);

The first statement cascades three adders in series. The second statement creates two adders in parallel: A1 + A2 and A3 + A4. In the second statement, the two additions are evaluated in parallel and the results are combined with a third adder. RTL simulation results are the same for both statements, however, the second statement results in a faster circuit after synthesis (depending on the bit width of the input signals).

### **Omit Initial Values**

Do not assign signals and variables initial values because initial values are ignored by most synthesis tools. The functionality of the simulated design may not match the functionality of the synthesized design.

For example, do not use initialization statements such as the following:

variable SUM:INTEGER:=0;

# **Selecting VHDL Coding Styles**

Because VHDL designs are often created by design teams, Xilinx recommends that you agree on a coding style at the beginning of your project. An established coding style allows you to read and understand code written by your fellow team members. Also, inefficient coding styles can adversely impact synthesis and simulation, which can result in slow circuits. Additionally, because portions of existing VHDL designs are often used in new designs, you should follow coding standards that are understood by the majority of HDL designers. This section of the manual provides a list of suggested coding styles that you should establish before you begin your designs.

### Selecting a Capitalization Style

Select a capitalization style for your code. In Xilinx FPGA designs, entity names must be in lowercase letters because the XACT*step* Development System does not recognize names in uppercase letters. Based on this restriction, you may want to specify that VHDL reserved words are in lowercase letters and other keywords are in uppercase letters.

The following capitalization style is used for the examples in this manual.

- Use lowercase letters for entity names and VHDL reserved words

- Use uppercase letters for the following:

- Keywords that are not entity names and VHDL reserved words

- Variable, signal, instance, and module names

- Labels

- Libraries, packages, and data types

- For the names of standard or vendor packages, follow the style used by the vendor or use uppercase letters as shown for IEEE in the following example:

```

library IEEE;

use IEEE.std_logic_1164.all;

signal SIG: UNSIGNED (5 downto 0);

```

### **Using Xilinx Naming Conventions**

Use the Xilinx naming conventions listed in this section for naming signals, variables, and instances that are translated into nets, buses, and symbols.

**Note:** Most synthesis tools convert illegal characters to legal ones.

- User-defined names can contain A-Z, a-z, \$, \_, -, <, and >. A "/" is also valid, however, it is not recommended since it is used as a hierarchy separator

- Names must contain at least one non-numeric character

Names cannot be more than 1024 characters long

The following FPGA resource names are reserved and should not be used to name nets or components.

- Configurable Logic Blocks (CLBs), Input/Output Blocks (IOBs), clock buffers, tristate buffers (BUFTs), oscillators, package pin names, CCLK, DP, GND, VCC, and RST

- CLB names such as AA, AB, and R1C2

- Primitive names such as TD0, BSCAN, M0, M1, M2, or STARTUP

- Do not use pin names such as P1 and P2 for component names

- Do not use pad names such as PAD1 for component names

**Note:** See the "Floorplanning Your Design" chapter for additional naming conventions that are important when using the Floorplanner.

### Naming Identifiers, Types, and Packages

You can use long (1024 characters maximum) identifier names with underscores and embedded punctuation in your code. Use meaningful names for signals and variables, such as CONTROL\_REGISTER. Use meaningful names when defining VHDL types and packages as shown in the following examples:

```

type LOCATION_TYPE is ...;

package STRING_IO_PKG is

```

### **Using Labels**

Use labels to group logic. Label all processes, functions, and procedures as shown in the following example:

ASYNC\_FF: process (CLK,RST)

You can use optional labels on flow control constructs to make the code structure more obvious, as shown in Figure 2-1. However, you should note that these labels are not translated to gate or register names in your implemented design.

```

-- D_REGISTER.VHD

-- Xilinx HDL Synthesis Design Guide for FPGA

-- June 1995

-- Changing Latch into a D-Register

entity d_register is

port (CLK, DATA: in BIT;

Q: out BIT);

end d_register;

architecture BEHAV of d_register is

begin

REG: process (CLK, DATA)

begin

if (CLK'event and CLK='1') then

Q <= DATA;

end if;

end process; --End REG

end BEHAV;

```

Figure 2-1 Labeling Flow Control Constructs

### **Using Variables for Constants**

Do not use variables for constants in your code. Define constant numeric values in your code as constants and use them by name. This coding convention allows you to easily determine if several occurrences of the same literal value have the same meaning. In the code example in Figure 2-2, you should specify the seven as a constant and refer to it by name in your code.

```

procedure FLOP

for I in 0 to 7 loop

FIELD(I) := FIELD(7-I);

end loop;

end procedure;

```

Figure 2-2 Defining Constants

### Using Named and Positional Association

Use positional association in function and procedure calls and in port lists only when you assign all items in the list. Use named association when you assign only some of the items in the list. Do not combine positional and named association in the same statement as illustrated in the following line of code:

```

CLK_1: BUFGS port map (I=>CLOCK_IN,CLOCK_OUT);

```

The correct coding style is:

```

CLK_1: BUFGS port map

(I=>CLOCK_IN,O=>CLOCK_OUT);

```

### **Managing Your Design**

As part of your coding specifications, you should include rules for naming, organizing, and distributing your files. Also, use explicit configurations to control the selection of components and architectures that you want to compile, simulate, or synthesize.

### **Creating Readable Code**

Use the recommendations in this section to create code that is easy to read.

#### **Indenting Your Code**

Indent blocks of code to align related statements. You should define the number of spaces for each indentation level and specify whether the Begin statement is placed on a line by itself. In the examples in this manual, each level of indentation is four spaces and the Begin statement is on a separate line that is not indented from the previous line of code. The example in Figure 2-3 illustrates the indentation style used in this manual.

```

architecture BEHAV of dlatch

begin

LATCH_P: process (A,B)

begin

if CONDITION then

STATEMENT;

else CONDITION

STATEMENT;

end if;

end process;--End LATCH_P

end BEHAV;

```

Figure 2-3 Indenting Your Code

#### **Using Empty Lines**

Use empty lines to separate top-level constructs, designs, architectures, configurations, processes, subprograms, and packages.

#### Using Spaces

Use spaces to make your code easier to read. The following conventions are used for the examples in this manual.

• You can omit or use spaces between signal names as shown in the following lines of code:

```

process (RST,CLOCK,LOAD,CE)

process (RST, CLOCK, LOAD, CE)

```

• Use a space after colons as shown in the following lines of code:

```

signal QOUT: STD_LOGIC_VECTOR (3 downto 0);

```

CLK\_1: BUFGS port map (I=>CLOCK\_IN,O=>CLOCK\_OUT);

#### Breaking Long Lines of Code

Break long lines of code at an appropriate point, such as a comma or a colon, to make your code easier to read, as illustrated in the following code fragment.

```

Ul: load_reg port map (INX=>A,LOAD=>LD,

CLK=>SCLK,OUTX=>B);

```

#### **Adding Comments**

Add comments to your code to improve readability, debugging, and maintenance.

### Using Std\_logic Data Type

**Note:** This section is an edited excerpt from a document in the Synopsys SOLV-IT! knowledge base. For more information on SOLV-IT, send e-mail to solvit@synopsys.com with the word help in the message body.

It is important to select the correct logic type for your VHDL designs. If you use the Synopsys compiler, the Std\_logic (IEEE 1164) type is recommended for synthesis. This type is effective for hardware descriptions because it has nine different values. Additionally, the Std\_logic type is automatically initialized to an unknown value. This automatic initialization is important for HDL designs because it forces you to initialize your design to a known state, which is similar to what is required in a schematic design. Do not override this feature by initializing signals and variables to a known value when they are declared because the result may be a gate-level circuit that cannot be initialized to a known value.

#### **Declaring Ports**

Xilinx recommends that you use the Std\_logic package for all entity port declarations. This package makes it easier to integrate the synthesized netlist back into the design hierarchy without requiring conversion functions for the ports. An example of using the Std\_logic package for port declarations is shown in Figure 2-4.

```

Entity alu is

port( A : in STD_LOGIC_VECTOR(3 downto 0);

B : in STD_LOGIC_VECTOR(3 downto 0);

CLK : in STD_LOGIC;

C : out STD_LOGIC_VECTOR(3 downto 0) );

end alu;

```

#### Figure 2-4 Using Std\_logic Package for Port Declaration

#### Minimizing the Use of Ports Declared as Buffers

Declare a buffer when a signal is used internally and as an output port. In the example in Figure 2-5, signal C is used internally and it is used as an output port.

```

Entity alu is

port( A : in STD_LOGIC_VECTOR(3 downto 0);

B : in STD_LOGIC_VECTOR(3 downto 0);

CLK : in STD_LOGIC;

C : buffer STD_LOGIC_VECTOR(3 downto 0) );

end alu;

architecture BEHAVIORAL of alu is

begin

process begin

wait until CLK'event and CLK='1';

C <= UNSIGNED(A) + UNSIGNED(B) + UNSIGNED(C);

end process;

end BEHAVIORAL;</pre>

```

Figure 2-5 Example of Buffer Output Signal

Because signal C is used both internally and as an output port, every level of hierarchy in your design that connects to port C must be declared as a buffer. To reduce the amount of coding in hierarchical designs, you may want to insert a dummy signal and declare port C as an output, as shown in Figure 2-6.

```

Entity alu is

port( A : in STD_LOGIC_VECTOR(3 downto 0);

B : in STD_LOGIC_VECTOR(3 downto 0);

CLK : in STD_LOGIC;

C : out STD_LOGIC_VECTOR(3 downto 0));

end alu;

architecture BEHAVIORAL of alu is

-- dummy signal

signal C_INT : STD_LOGIC_VECTOR(3 downto 0);

begin

C <= C_INT;

process begin

wait until CLK'event and CLK='1';

C_INT < =UNSIGNED(A) + UNSIGNED(B) +

UNSIGNED(C_INT);

end process;

end BEHAVIORAL;

```

#### Figure 2-6 Replacing Buffer Ports with a Dummy Signal

### **Comparing Signals and Variables**

**Note:** This section is an edited excerpt from a document in the Synopsys SOLV-IT! knowledge base. For more information on SOLV-IT, send e-mail to solvit@synopsys.com with the word help in the message body.

You can use signals and variables in your designs. Signals are similar to hardware and are not updated until the end of a process. Variables are immediately updated and, as a result, they can mask glitches that may impact how your design functions. Because of this potential masking problem, Xilinx recommends that you use signals for hardware descriptions, however, variables allow quick simulation. Figure 2-7 shows a synthesized design that uses signals and Figure 2-8 shows a synthesized design that uses variables. These examples are shown implemented with gates in Figure 2-9 and Figure 2-10. **Note:** If you assign several values to a signal in one process, only the final value is used. When you assign a value to a variable, the assignment takes place immediately. A variable maintains its value until you specify a new value.

#### **Figure 2-7 Using Signals**

Figure 2-8 Using Variables

Figure 2-9 Gate implementation of Xor\_Sig

Figure 2-10 Gate Implementation of Xor\_Var

## **Using Schematic Design Hints with HDL Designs**

This section describes how you can apply schematic entry design strategies to HDL designs.

## **Barrel Shifter Design**

The schematic version of the barrel shifter design is included in the "Multiplexers and Barrel Shifters in XC3000/XC3100" application note (XAPP 026.001) in the 1994 version of *The Xilinx Programmable Logic Data Book*. In this example, two levels of multiplexers are used to increase the speed of a 16-bit barrel shifter. This design is for XC3000 and XC3100 devices; however, it can also be used for XC4000 devices. This section includes two VHDL versions of the barrel shifter design.

**Note:** In the 16-bit barrel shifter example in the XAPP 026.001 application note, the select lines are registered to take advantage of the CLB DIN pin. You do not need to register the select lines in your HDL design because most synthesis tools do not use the DIN pin.

Figure 2-11 is a VHDL design of a 16-bit barrel shifter. The barrel shifter is implemented using sixteen 16-to-1 multiplexers, one for each output. A 16-to-1 multiplexer is a 20-input function with 16 data inputs and four select inputs. When targeting an FPGA device based

on 4-input lookup tables (such as XC4000 and XC3000 devices), a 20-input function requires at least five logic blocks. Therefore, the minimum design size is 80 (16 x 5) logic blocks.

```

-- THIS EXAMPLE IS FOR COMPARISON ONLY

-- June 1995

--

___

-- USE barrel.vhd

--

_____

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

entity barrel_org is

port (S: in STD_LOGIC_VECTOR (3 downto 0);

A_P: in STD_LOGIC_VECTOR (15 downto 0);

B_P: out STD_LOGIC_VECTOR (15 downto 0));

end barrel_org.

end barrel_org;

architecture RTL of barrel_org is

begin

SHIFT: process (S, A_P)

begin

in

case S is

when "0000" =>

B_P

<= A_P;

when "0001" =>

B_P(14 downto 0) <= A_P(15 downto 1);

B_P(15) <= A_P(0);

when "0010" =>

B_P(13 downto 0) <= A_P(15 downto 2);

B_P(15 downto 14) <= A_P(1 downto 0);</pre>

when "0011" =>

B_P(12 downto 0) <= A_P(15 downto 3);

B_P(15 downto 13) <= A_P(2 downto 0);</pre>

when "0100" =>

B_P(11 downto 0) <= A_P(15 downto 4);

B_P(15 downto 12) <= A_P(3 downto 0);

when "0101" =>

B_P(10 downto 0) <= A_P(15 downto 5);

B_P(15 downto 11) <= A_P(4 downto 0);</pre>

when "0110" =>

B_P(9 downto 0) <= A_P(15 downto 6);

B_P(15 downto 10) <= A_P(5 downto 0);

```

```

when "0111" =>

B_P(8 downto 0) <= A_P(15 downto 7);

B_P(15 downto 9) <= A_P(6 downto 0);

when "1000" =>

B_P(7 downto 0) <= A_P(15 downto 8);

B_P(15 downto 8) <= A_P(7 downto 0);

when "1001" =>

B_P(6 downto 0) <= A_P(15 downto 9);

B_P(15 downto 7) <= A_P(8 downto 0);

when "1010" =>

B_P(5 downto 0) <= A_P(15 downto 10);

B_P(15 downto 6) <= A_P(9 downto 0);

when "1011" =>

B_P(4 downto 0) <= A_P(15 downto 11);

B_P(15 downto 5) <= A_P(10 downto 0);

when "1100" =>

B_P(3 downto 0) <= A_P(15 downto 12);

B_P(15 downto 4) <= A_P(11 downto 0);

when "1101" =>

B_P(2 downto 0) <= A_P(15 downto 13);

B_P(15 downto 3) <= A_P(12 downto 0);

when "1110" =>

B_P(1 downto 0) <= A_P(15 downto 14);

B_P(15 downto 2) <= A_P(13 downto 0);

when "1111" =>

B_P(0) <= A_P(15);

B_P(15 downto 1) <= A_P(14 downto 0);

when others =>

B_P

<= A_P;

end case;

end process; -- End SHIFT

```

end RTL;

#### Figure 2-11 16-bit Barrel Shifter

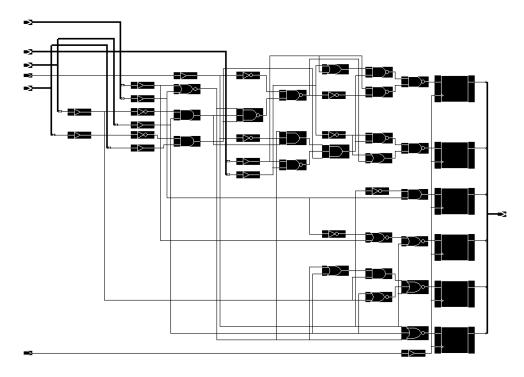

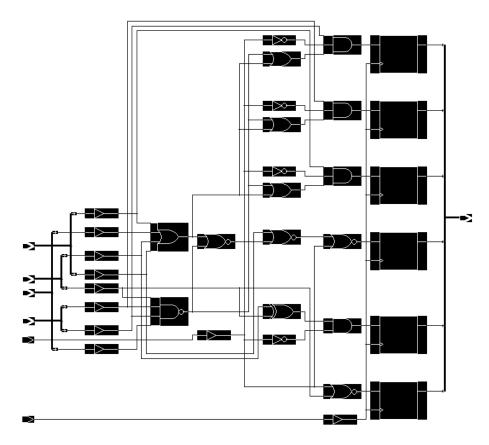

The modified VHDL design in Figure 2-12 uses two levels of multiplexers and is twice as fast as the design in Figure 2-11. This design is implemented using 32 4-to-1 multiplexers arranged in two levels of sixteen. The first level rotates the input data by 0, 1, 2, or 3 bits and the second level rotates the data by 0, 4, 8, or 12 bits. Since you can build a 4-to-1 multiplexer with a single logic block, the minimum size of this version of the design is 32 (32 x 1) logic blocks.

```

-- XAPP 26 (1994 Data Book p. 8-152)

-- 16-bit barrelshifter (shift right)

-- 2 November 94

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

end barrel;

architecture RTL of barrel is

signal SEL1,SEL2: STD_LOGIC_VECTOR (1 downto 0);

signal C: STD_LOGIC_VECTOR (15 downto 0);

begin

FIRST_LVL: process (A_P, SEL1)

begin

n

case SEL1 is

when "00" => -- Shift by 0

<= A_P;

when "01" => -- Shift by 1

C(15) <= A_P(0);

C(14 downto 0) <= A_P(15 downto 1);

when "10" => -- Shift by 2

C(15 downto 14) <= A_P(1 downto 0);

C(13 downto 0) <= A_P(15 downto 2);

when "11" => -- Shift by 3

C(15 downto 13) <= A_P(2 downto 0);

C(12 downto 0) <= A_P(15 downto 3);</pre>

when others =>

<= A_P;

С

end case;

end process; --End FIRST_LVL

SECND_LVL: process (C, SEL2)

begin

case SEL2 is

when "00" => --Shift by 0

B_P <= C;

when "01" => --Shift by 4

B_P(15 downto 12) <= C(3 downto 0);

B_P(11 downto 0) <= C(15 downto 4);

when "10" => --Shift by 8

B_P(7 downto 0) <= C(15 downto 8);

B_P(15 downto 8) <= C(7 downto 0);

when "11" => --Shift by 12

B_P(3 downto 0) <= C(15 downto 12);

B_P(15 downto 4) <= C(11 downto 0);

```

### Figure 2-12 16-bit Barrel Shifter with Two Levels of Multiplexers

When these two designs are implemented in an XC4005-5 device using the Synopsys FPGA compiler, there is a 54% improvement in the gate count (91 occupied CLBs reduced to 36 occupied CLBs) in the design in Figure 2-12 as compared to the design in Figure 2-11. Additionally, there is a 25% improvement in speed from 54.2 ns (4 CLB block levels) to 46.4 ns (3 CLB block levels).

### Implementing Latches and Registers

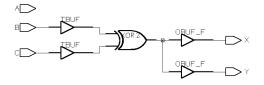

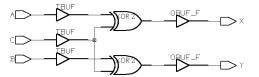

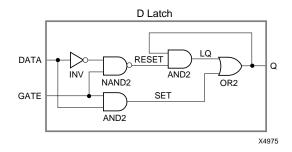

HDL compilers infer latches from incomplete specifications of conditional expressions. Latch primitives are not available in CLBs, however, the IOBs contain input latches. Latches described in RTL HDL are implemented with gates in the CLB function generators. For example, the D latch shown in Figure 2-13 is implemented with one function generator. The D latch implemented with gates is shown in Figure 2-14.

```

-- D_LATCH.VHD

-- Xilinx HDL Synthesis Design Guide for FPGAs

-- June 1995

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity d_latch is

port (GATE, DATA: in STD_LOGIC;

Q: out STD_LOGIC);

end d_latch;

architecture BEHAV of d_latch is

begin

LATCH: process (GATE, DATA)

begin

if (GATE = '1') then

Q <= DATA;

end if;

end process; -- end LATCH

end BEHAV;

```

#### Figure 2-13 D Latch Inference

#### Figure 2-14 D Latch Implemented with Gates

In this example, a combinatorial loop results in a hold-time requirement on DATA with respect to GATE. Since most synthesis tools do not process hold-time requirements because of the uncertainty of routing delays, Xilinx does not recommend implementing latches with combinatorial feedback loops. A recommended method for implementing latches is described in this section. When you run the Partition, Place, and Route (PPR) program on the example in Figure , the following warning message appears.

\*\* Warning: [tspec: COMBINATIONAL\_LOOPS] This design has 1 purely combinational loop. Such loops should be avoided. If at all possible, please modify the design to eliminate all unclocked feedback paths.

To eliminate this warning message, use D registers instead of latches. For example, in the code example in Figure 2-13, to convert the D latch to a D register, use an Else statement, a Wait Until statement, or modify the code to resemble the code in Figure 2-15.

In the example in Figure 2-15, you can use a Wait Until statement instead of an If statement, however, use an If statement when possible because it gives you more control over the inferred register's capabilities. For more information on latches and registers, refer to the Synopsys VHDL compiler documentation.

```

-- D_REGISTER.VHD

-- Xilinx HDL Synthesis Design Guide for FPGA

-- June 1995

-- Changing Latch into a D-Register

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity d_register is

port (CLK, DATA: in STD_LOGIC;

Q: out STD_LOGIC);

end d_register;

architecture BEHAV of d_register is

begin

REG: process (CLK, DATA)

begin

if (CLK'event and CLK='1') then

Q <= DATA;

end if;

end process; --End REG

end BEHAV;

```

#### Figure 2-15 Converting a D Latch to a D Register

If you are using the Synopsys Design Compiler or FPGA Compiler, you can determine the number of latches that are implemented when your design is read with the following command:

```

hdlin_check_no_latch = "TRUE"

```

When you set this command to true, a warning message is issued when a latch is inferred from a design. Use this command to verify that a combinatorial design does not contain latches. The default value for this command is false.

You should convert all If statements without corresponding Else statements and without a clock edge to registers. Use the recommended register coding styles in the synthesis tool documentation to complete this conversion.

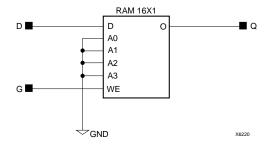

In XC4000 devices, you can implement a D latch by instantiating a RAM 16x1 primitive, as illustrated in Figure 2-16.

Figure 2-16 D Latch Implemented by Instantiating a RAM

In all other cases (such as latches with reset/set or enable), use a D flip-flop instead of a latch. This rule also applies to JK and SR flip-flops.

Table 2-1 provides a comparison of area and speed for a D latch implemented with gates, a 16x1 RAM primitive, and a D flip-flop.

|                                         | D Latch                                                                                                                             | XC4000 RAM 16x1<br>Primitive                                                                       | D Flip-Flop                                                                                                            |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Advantages/<br>Disadvantages            | RTL HDL that infers<br>D latch implemented<br>with gates. Combina-<br>torial feed-back loop<br>results in hold-time<br>requirement. | Structural HDL.<br>Instantiated RAM 16x1<br>primitive.<br>No hold time or com-<br>binatorial loop. | Requires change to the<br>RTL HDL to convert D<br>latches to D flip-flops.<br>No hold time or com-<br>binatorial loop. |

| Area <sup>1</sup><br>Speed <sup>2</sup> | 1 Function Generator<br>1 Logic Level;                                                                                              | 1 Function Generator<br>1 Logic Level; no com-                                                     | 1 Register<br>1 Logic Level; no com-                                                                                   |

|                                         | combinatorial feed-<br>back loop.                                                                                                   | binatorial loop.                                                                                   | binatorial loop.                                                                                                       |

Table 2-1 D Latch Implementation Comparison

<sup>1</sup>Area is the number of function generators and registers required. Each CLB has two function generators and two registers in XC4000 devices. <sup>2</sup>Speed is the number of CLB logic levels required.

## **Resource Sharing**

Resource sharing is an optimization technique that uses a single functional block (such as an adder or comparator) to implement several operators in the HDL code. Use resource sharing to improve design performance by reducing the gate count and the routing congestion. If you do not use resource sharing, each HDL operation is built with separate circuitry. However, you may want to disable resource sharing for speed critical paths in your design.

The following operators can be shared either with instances of the same operator or with the operator on the same line.

\* + -> >= < <=

For example, a + operator can be shared with instances of other + operators or with - operators.

You can implement arithmetic functions (+, -, magnitude comparators) with gates, Synopsys DesignWare functions, or Xilinx

DesignWare functions. The Xilinx DesignWare functions use X-BLOX modules that take advantage of the carry logic in XC4000 CLBs. XC4000 carry logic and its dedicated routing increase the speed of arithmetic functions that are larger than 4-bits. To increase speed, use the Xilinx X-BLOX DesignWare library if your design contains arithmetic functions that are larger than 4-bits or if your design contains only one arithmetic function. Resource sharing of the Xilinx DesignWare library automatically occurs if the arithmetic functions are in the same process.

Resource sharing adds additional logic levels to multiplex the inputs to implement more than one function. Therefore, you may not want to use it for arithmetic functions that are part of your design's critical path.

Since resource sharing allows you to reduce the number of design resources, the device area required for your design is also decreased. The area that is used for a shared resource depends on the type and bit width of the shared operation. You should create a shared resource to accommodate the largest bit width and to perform all operations.

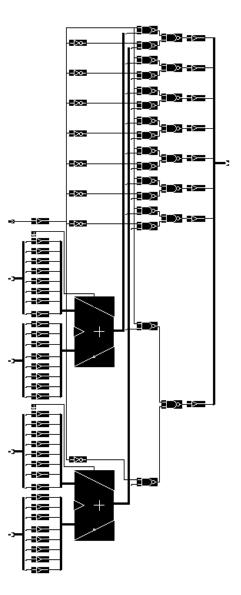

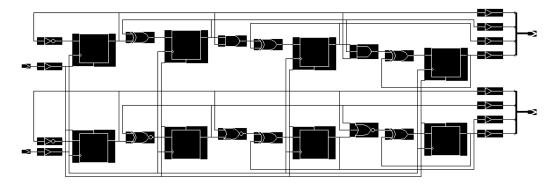

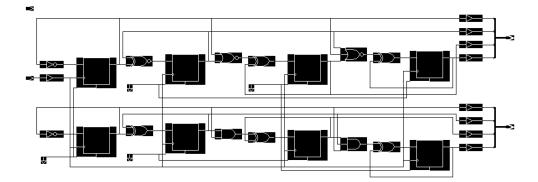

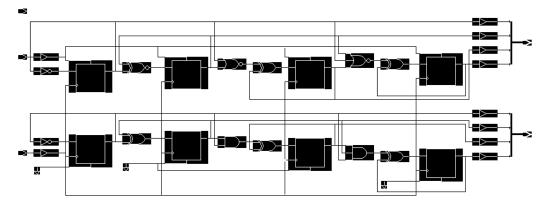

If you use resource sharing in your designs, you may want to use multiplexers to transfer values from different sources to a common resource input. In designs that have shared operations with the same output target, the number of multiplexers is reduced as illustrated in Figure 2-17. The HDL example in Figure 2-17 is shown implemented with gates in Figure 2-18.

#### Figure 2-17 Resource Sharing

Xilinx Development System

Figure 2-18 Implementation of Resource Sharing

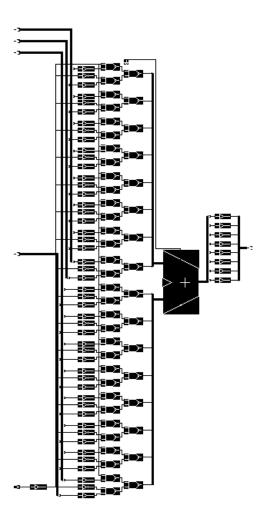

If you disable resource sharing with the Hdl\_resource\_allocation = none command or if you code the design with the adders in separate processes, the design is implemented using two X-BLOX modules as shown in Figure 2-19.

Xilinx Development System

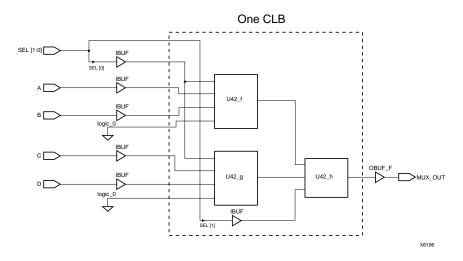

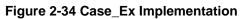

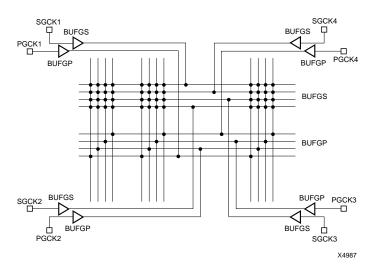

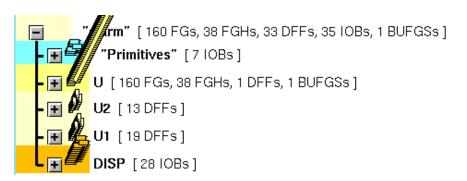

Table 2-2 provides a comparison of the number of CLBs used and the delay for the design in Figure 2-17 with and without resource sharing. The last column in Table 2-2 provides CLB and delay information for the same design with resource sharing and without X-BLOX modules.