# EE 552 Project Smart Audio Equalizer Final Report

David R. Bull bull@ee.ualberta.ca

Dustin R. Demontigny demontig@ee.ualberta.ca

March 27, 2003

# **Declaration of Content**

The design elements of this project and report are entirely the original work of the authors and have not been submitted for credit in any other course, except for the following:

| vill be using V.<br>o Signals Throu |      |        | Inputting  | and | Output | ting |

|-------------------------------------|------|--------|------------|-----|--------|------|

|                                     |      |        |            |     |        |      |

|                                     |      |        |            |     |        |      |

|                                     |      |        |            |     | _      |      |

| David R.                            | Bull | Dustir | n Demontig | ny  |        |      |

|                                     |      |        |            |     |        |      |

Date

# **Abstract**

This report describes the design and implementation of a smart audio equalizer system. The equalizer is a 2-channel, 10 band audio equalizer using the XSA-100 + Xstend prototyping board. The stereo audio codec on the XS-tend board digitizes the analog audio and constructs a digital bitstream. The audio equalizer can be customized by the user to best suit his or her individual hearing characteristics. The system optimizes the audio signal generated in real time to best suit each listener. The hardware components used are described in detail as well as the current VHDL source code including simulation waveforms and test benches.

# Contents

| 1         | Achievements                                          | 1                  |  |  |  |

|-----------|-------------------------------------------------------|--------------------|--|--|--|

| 2         | Introduction                                          | 1                  |  |  |  |

| 3         | Design Concept                                        | 2                  |  |  |  |

| 4         | Stereo Audio Codec           4.1 Codec Interface      | <b>3</b><br>3<br>4 |  |  |  |

| 5         | Filter Subsystem                                      | 4                  |  |  |  |

| 6         | RAM Loader                                            | 5                  |  |  |  |

| 7         | User Interface 7.1 Description                        | <b>5</b><br>5      |  |  |  |

| 8         | Arithmetic Unit           8.1 Description             | <b>7</b><br>7<br>7 |  |  |  |

| 9         | FPGA Requirements                                     | 11                 |  |  |  |

| 10        | Experiments and Characterization                      | 12                 |  |  |  |

| 11        | External Sources                                      | 14                 |  |  |  |

| <b>12</b> | 2 Datasheets                                          |                    |  |  |  |

| 13        | 13 Design Verification 1                              |                    |  |  |  |

| 14        | Design Hierarchy                                      | 55                 |  |  |  |

| <b>15</b> | VHDL Code                                             | 57                 |  |  |  |

| 16        | Test Benches                                          | 130                |  |  |  |

| 17        | Schematics                                            | 155                |  |  |  |

| 18        | Inputting/Outputting Stereo Signals Through the Codec | 158                |  |  |  |

### 1 Achievements

The first design of our digital filter module was not very good. The old design instantiated a multiplier and adder for each filter tap and consumed a large portion of the logic resources. A second filter design implements a larger filter with higher resolution at the cost of 1/3 the hardware. This was a very good achievement.

The new filter design works beautifully in simulation, unfortunately, at this point we have been unable to get it working on the board. We have spent many hours debugging the problem but have not yet reached a solution. We are hopeful that we will get something working before the end of the term.

We were successful, however, in getting the first design of our digital filter to produce valid output given a set of test data. This experiment is outlined in the testing section of this report.

The current version of the user interface successfully reads the inputs from 3 pushbuttons to control the state and gain settings of the smart equalizer system. The user toggles between the preset value using the incr or decr pushbuttons. The system can be reset with the third push button. The preset number is displayed using the seven segment LED display on the left side of the XStend board. The gain vector is sent to the arithmetic unit.

An arithmetic unit has been added to the smart equalizer system since the creation of the simulation report. This section of the code evaluates the coefficients needed by the filter block using the tap and gain values. This section has no connection with the outside world. It serves as the interface between the user I/O and the filter block. The description of operation is described in more detail in the following sections. Test benches used to simulate the arithmetic unit are attached in the Design and Verification section.

#### 2 Introduction

The human ear responds differently to sounds at various frequencies. In general, the ear is most sensitive to sounds at frequencies near 1kHz and

becomes increasingly insensitive as the the frequency deviates from this range[1]. Using an equalizer we can amplify the components of the signal we have difficulty hearing. Our smart equalizer will allow the user to configure the system to best suit his or her individual hearing characteristics providing the user with the best listening experience.

# 3 Design Concept

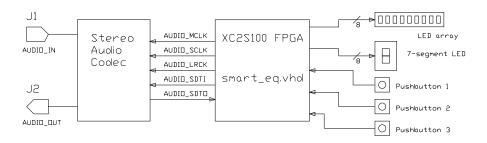

The proposed project will incorporate the XSA-100 + XStend project board, with an on-board stereo audio codec, to implement a 2-channel, 10-band audio equalizer. The gain for each band will be adjusted manually by the user. The top level diagram of the system is shown in Figure 1.

Figure 1: Top Level Diagram

The system inputs a stereo audio signal into the stereo codec. The codec runs off of three clock signals provided by the circuitry in the FPGA; mclk, sclk and lrck. The digitized audio samples are fed into the FPGA through the sdout pin. The top level entity in the FPGA,  $smart\_eq.vhd$ , will filter the input samples and send them serially to the audio codec via the sdin pin. The reconstructed analog audio signal is output from the audio codec.

User input will be obtained with the use of pushbuttons and dip-switches. There are four on-board pushbuttons, only three of which are accessible for general purpose input, and 12 dip-switches. Since only three pushbuttons is insufficient for this system, we will use the dipswitches to set a "mode" for which the pushbuttons will operate. This way, we can effectively create

$3*2^n$  pushbutton inputs, using 3 bushbuttons and n dip-switches. We will only use one dip-switch.

A 7-segment LED display and an 8-segment LED bargraph will be used do display the status of the system and to guide the user.

The equalizer system is divided into three main sections:

- 1. A codec interface (codec\_intfc.vhd)

- 2. A filter module (filter.vhd)

- 3. A user interface (user\_io.vhd)

The operation of these subsystems is described in the sections that follow.

## 4 Stereo Audio Codec

The XStend board includes a 20-bit stereo audio codec that digitizes a two channel analog signal while simultaneously reconstructing a two channel analog signal. A high level diagram of the codec chip is shown in [5]. The codec chip includes a series of 20-bit shift registers used to serially transfer sample values to and from the FPGA. The codec interface will also include a series of 20-bit shift registers as well as circuitry to read and write to them.

#### 4.1 Codec Interface

The XStend Board V1.3.2 User Manual includes documentation and VHDL code for a codec interface circuit (codec\_intfc.vhd) used to send and received data to and from the stereo audio codec. This document is included in Appendix 18. Our system will incorporate this codec interface circuit.

The codec interface is composed of two modules:

- A clock generator module (clk\_gen.vhd) which generates and outputs the codec clock signals, and

- A channel module (*channel.vhd*) which contains the shift registers and control circuitry for a single serial stream of input/output data.

These two modules are integrated together to form the codec interface circuit.

The sample code was revised to change the reset signal from active-high asynchronous to active-low synchronous, since the reset signal will be triggered using an active-low pushbutton. Also, the *bit\_cntr* signal was included as an output of the *codec\_intfc* module so that it can be used in the filter module. The revised code is included in Appendix 15.

#### 4.2 Clock Generator

Three clock signals must be provided to the codec chip.

- 1. mclk master clock to codec

- 2. sclk serial data clock

- 3. lrck left/right codec channel select

For sampling frequency  $f_s$ , the clock signals are related as follows:

```

mclk = 256f_s

sclk = 64f_s

lrck = f_s

```

Taking mclk = 100MHz/8 = 12.5MHz, we get a sampling frequency of  $f_s = 48.8KHz$ .

# 5 Filter Subsystem

Consider the simplified schematic on the following page. The filter is composed of two counters (counter and counterd), two single port distributed RAMs (distram), a signed multiplier (fmult) and an accumulator (facc). One RAM holds the filter coefficients and the other holds the sample values. The RAM holding the sample values is twice the size of the RAM holding the filter coefficients. The top half holds the sample values for the left channel and the bottom half holds the sample values for the right channel. The input to the coefficient RAM is fed by a RAM loader, which is discussed in the following section. The sample RAM inputs digitized samples from the codec interface.

The counters hold the RAM addresses. When an audio sample is received from the codec interface it is loaded into the sample RAM and the address counters are enabled. The RAMs loop throught and multiply the coefficients with the corresponding sample values. The result is stored in the accumulator. The accumulator is reset after the value at the output of the filter is read.

#### 6 RAM Loader

A device which we call a RAM loader is used to load the filter coefficients into the RAM. See the following page for a simplified schematic. A slightly modified RAM loader is also used to initialize the contents of the sample RAM. The RAM loaders use several handshaking signals. When data is ready to be loaded into the RAM the  $data\_in\_rdy$  signal is asserted. The RAM loader requests control of the RAM control signals (address, write enable, etc.) by asserting  $cont\_req$ . The RAM is granted control when the  $cont\_ack$  signal is asserted. And finally, when the RAM loader has finished it asserts both the  $cont\_rel$  and  $data\_in\_ack$  signals.

### 7 User Interface

## 7.1 Description

The smart equalizer has a user interface that allows interaction between the equalizer parameters and the outside world. The hardware components used in the user interface include 3 pushbuttons and a seven segment LED display, which are all accessible on the XStend board.

The user can select a preset value for the band gains. Two pushbuttons are used to cycle up or down between the desired preset values. Preset 0 will create an equalizer with a flat response (unity gain). Preset 1 will correspond to user 1 (i.e.Dave's setting), preset 2 to user 2 and so on. The current preset will be displayed on the 7 segment display.

The user interface manipulates input data from the outside world and stores band gain values in a register for use in the filter subsystem. It is important to note here that the User Interface is not channel dependent. In other words it applies the same gain to the left channel as it does to the right channel.

#### 7.2 Implementation

The user interface incorporates four main components: a debouncer, a preset counter, a preset decoder and a bcd decoder. These four components are instantiated structurally in one VHDL file user\_io.vhd which is the top level for the user interface. The project package file, smart\_eq\_pack.vhd holds all of the constants and component declarations used in the user interface.

The debounce entity described in debouncer3.vhd removes unwanted transients from the pushbutton inputs creating stable pulses of varying width. It does this by counting the number of clock cycles that occur. When the number of clock cycles (count) reaches the required value set by the constant (debounce\_delay), the input signals are mapped to the output. This method works well as long as the debounce delay is greater than the maximum bounce duration of the pushbuttons. It is important to mention here that a debounce\_delay of 7 was used for simulation purposes whereas a debounce duration of 1023 will be used when implementing the design on the FPGA. The outputs from the debouncer are sent to the input of the preset counter.

The preset counter is decribed in preset\_counter.vhd. This component reads the input pushbuttons to set the desired preset value. It works similar to an up down counter. When (incr) is pressed the preset value is incremented by one. Similarily, when (decr) is pressed the preset value is decremented by one. A synchronous reset button is used to set the preset value to zero. A very important requirement is to allow the preset value to increment or decrement only once for every press cycle. This requirement is fullfilled by using (press) variables to be used on the pushbuttons. These variables act as a flags to indicate when the pushbutton signals goes low. These flags are then checked whenever the pushbuttons are not low. If the flags are set, then the preset value is incremented or decremented accordingly and the flag is reset to zero. It is important to note here that this system relies on only one pushbutton being pressed at one time. This requirement is acceptable considering the manner in which the user interface is used.

The output from the preset counter is sent to two decoders: a bcd decoder and a preset decoder. These are described in files bcd\_decoder.vhd and preset\_decoder.vhd respectively. The bcd decoder takes the value of the

preset counter and converts it to a decimal number display on the seven segment LED display. The preset decoder converts the value of the preset counter to a vector of gain values. This vector is sent to the arithmetic unit to calculate the resulting filter coefficients for the filter block. The configuration of the LED segments and the preset values are stored in the package file smart\_eq\_pack.vhd and can be changed or updated as needed.

# 8 Arithmetic Unit

### 8.1 Description

The smart equalizer uses an arithmetic unit to calculate the filter coefficients. The inputs to the arithmetic unit include the gain values for all bands from the user interface and the hard coded filter taps listed in the top level package file smart\_eq\_pack.vhd. The arithmetic unit calculates the values of each of the filter coefficients and sends them to the filter block eq. The arithmetic unit has no external FPGA connections.

#### 8.2 Implementation

The arithmetic unit uses five components: two temporary registers, a multiplier, an accumulator and a register controller. These five components are instantiated structurally in one VHDL file arith\_unit.vhd. The project package file, smart\_eq\_pack.vhd holds all of the constants and component declarations used in the arithmetic unit.

The first temporary register is used to shift the gain vector input and output the require gain of each band, one at a time. The signal aload inputs the whole vector into the register. The clock signal shifts the register to the right by one gain value (usually 4 bits). The output is the least significant 4 bits, which is equivalent to the gain of the selected band.

Every time the register switches from one band to the next, the coef\_value changes. This is performed using a process inside the arithmetic unit that increments the tap number. The value of signal coef\_value is equal to the tap\_number element in the tap array declared in the package file. Essentially this performs as an on chip ROM device.

The multiplier takes the coef\_value from the on chip ROM and multiplies it by the band gain. The output of the multiplier has the same number of bits as the signal coef\_value. It does this by simply truncating the output value by the number of bits in the band gain value.

The accumulator takes the output from the multiplier and creates a running sum of the signal vectors. It performs as many accumulations as there are bands (usually 10). Once it has performed these ten accumulations, it is cleared to zero and starts accumulating the values for the next coefficient. The output from the accumulator is sent to the second temporary register.

The second temporary register grabs the coefficient values from the accumulator and stores them in an array of vectors which are sent to the filter block. The array length is determined by the number of coefficients (number of filter taps plus one). The length of the coefficients is determined by the resolution of the filter (usually 12 bits).

The arithmetic unit is controlled by the entity reg\_control.vhd. It performs similar to a state machine. It controls the loading and shifting of the first temporary register as wells as the accumulation function and the storage of the coefficients stored in the second temporary register. After each individual coefficient is loaded into the array of vectors in the second temporary register, it shifts the gain to the beginning (least significant four bits), clears the accumulator, and starts calculations for the next coefficient.

# 9 FPGA Requirements

The revised filter design, as predicted, has drasticly reduced the logic requirements for our project.

The first filter design implemented two discrete  $6^{th}$  order FIR filters with 16-bit audio samples and 8-bit filter coefficients. Each filter contained 7  $16 \times 8$  bit multipliers (one for each filter tap) and 7, 20-bit adders to sum the products. Obviously the resource requirements for this design were quite significant. This design used over 90% of the logic resources (including codec interface).

The new filter design implements two  $10^{th}$  order FIR filters using circular buffers in RAM and a single multiplier and accumulator. We use 20-bit audio samples and 12-bit filter coefficients. The filter, codec interface and control circuitry for this design only consume 26% of the logic resources. In this case we have essentially doubled the size of the filter and we use only 1/3 the hardware.

The second module is the user interface. This module tests the functionality of the user input pushbuttons and dip switch and verifies proper operation using the seven segment display, LED bargraph. This module consumes 15% of the FPGA resources.

The user interface was also redesigned. The original architecture did not seperate the module into a controller and datapath. It consumed 27% of the FPGA resources, which was much more than originally scheduled. This required us to rethink the design and change the interface to toggle between preset values. The redesign, although costly in terms of timeline, resulted in a significant decrease in FPGA resources. The current version of the user interface (user\_io.vhd), which uses a preset counter, uses 14% of the FPGA requirements. This is reasonable considering the size of the gain register. The user interface could be enhanced if time and space permits. Reducing the size of the user interface would be quite difficult. Lowering the debounce delay, optimizing the preset counter and using RAM to store the gain values could possibly reduce the FPGA resource requirements of the user interface.

An arithmetic unit has been added to the smart equalizer system since the writing of the simulation documentation. This module is used to store the

tap values and evaluate the filter coefficients using the gain values. This unit stores the tap values in a ROM listed in the top level package file smart\_eq\_pack.vhd. The arithmetic unit uses 17% of the logic resources of the FPGA.

The top level smart equalizer system occupies 53% of the logic blocks of the FPGA. This is much less than the original filter and user interface design which took up 90% and 27% respectively. This is quite an improvements since the original filter was for a single band, and the user interface was slow and unreliable. The remaining 47% of the FPGA could be used to implement the enhancements listed in previous reports. Examples of these further enhancements include real time automatic optimization and VGA graphic equalizer display.

# 10 Experiments and Characterization

Since the new filter design uses RAM we tested the two different RAM types, distributed RAM and block RAM. Block RAM uses dedicated RAM blocks (there are 10 4K RAM blocks in the XC2S100 FPGA) and distributed RAM is implemented in the logic resources. Since we only use approximately 840 bits of RAM in total we chose to use distributed RAM. It was also easier to use the distributed RAM since the RAM can be read asynchronously. The implementation of the distributed RAM used minimal logic resources (i.e. only a few percent).

The structure of the user interface changed drastically during the development of the smart equalizer. Originally, the whole system including datapath and controller were linked into one file. The inputs were debounced in a seperate entity and instantiated structually in the top level. The original layout used 27% of the logic cells on the FPGA and operated quickly, although unreliably. For this reason, the datapath and controller of the user interface were seperated into datapath and controller sections in order to simply the layout and improve stability.

Two debounce mechanisms were designed in order to determine the best alternative. One used a counter that started counting once the signal went high. After the counter reached a certain value (say 1023) the output went high if the input remained high during the count sequence. Otherwise the

output stayed low. This design is demonstrated in debouncer.vhd. This implementation used 17 logic blocks in the FPGA.

The second debounce mechanism used an enable signal that was pulsed high every couple thousand clock cycles. The input is latched to the output on the rising edge of this enable signal. This method proved to be much more efficient than the previous design using only 12 logic blocks. The VHDL code for this debouncer can be seen in debouncer2.vhd. Both debouncers are used during the simulation and testing of the project components to observe how they affect the reliability and operation of the system.

Both versions of the debouncer use the same amount of clock cycles to delay the input. This allowed us to determine that the second implementation was more efficient since it used less of the FPGA resources but operated at the same speed. The speed of the user interface isn't as critical as it's reliablity since it is used to manipulate the parameters of the filters in the equalizer.

The user interface was changed later to reduce FPGA requirements and speed up operation. The current version of the user interface occupies approximately 15% of the logic resources of the FPGA. This is just over half of the original version. Most of the large registers and MUX devices were removed. This limited the abilities of the user but simplified the design creating a mechanism that was more reliable. The reduced size on the IC is also a bonus.

During the simplification of the filter system, the coefficient requirements were changed. The updated filter only needs as many coefficients as there are taps. This reduces the previous amount by a factor equal to the number of bands (in our case 10). The new coefficients are calculated using the arithmetic unit. This unit occupies 17% of the FPGA which is not very much considering it stores all of the tap values and stores the resultant coefficient. The arithmentic unit provides the interface between the filter and the user interface.

## 11 External Sources

As mentioned previously, the XStend Board V1.3.2 Manual includes the VHDL code for a codec interface circuit. This module is used in our system with slight modifications. The modified VHDL source code (loopback.vhd, codec\_intfc.vhd, clkgen.vhd and channel.vhd) can be found in Appendix 15.

Modifications to the sample code include changing the reset signal from active-high asynchronous to active-low synchronous, since the reset signal will be triggered using an active-low pushbutton. The bit\_cntr signal was included as an output of the codec\_intfc module so that it can be used in the filter module.

When compiling the sample code we came across an error. In the loopback.vhd file the signals *left\_channel* and *right\_channel* were only allocated 8 bits when they were expected to carry 20-bit signals. A simple correction of the vector indicies corrected the problem.

# References

- [1] Multimedia Signals and Systems, Mrinal Kr. Mandal, Kluwer Academic Publishers, 2003

- [2] Signal Processing and Linear Systems, Lathi, B.P., Berkeley Cambridge Press, 1998.

- [3] Discussions with Dr. Behrouz Nowrouzian, Electrical and Computer Engineering, University of Alberta.

- [4] Implementation of an Audio Filter on an FPGA Board, Herbertz, Kay, March 2002.

- [5] XStend Board V1.3.2 Manual, XESS Corporation, 2001.

- [6] Xstend Board V2.0 Manual, XESS Corporation, 2002.

- [7] Xilinx Synthesis Technology (XST) User Guide, Xilinx Inc.

# 12 Datasheets

The only device peripheral to the FPGA is the on-board stereo audio codec. The codec features a 20-bit analog to digital converter and digital to analog converter. The digitized audio samples are read from and written to serially. The coverpage for the codec datasheet is included on the following page. A schematic of the interface to the codec chip is included in Appendix 17.

# 13 Design Verification

# **Index of Test Cases**

| Case 1:  | Board hardware is tested by displaying counter value on the | 19 |

|----------|-------------------------------------------------------------|----|

|          | on-board LED displays                                       |    |

| Case 2:  | On-board audio codec is tested using the loopback circuit   | 19 |

|          | provided in XStend V1.3.2 Manual                            |    |

| Case 3:  | Loopback circuit is tested with real audio signals          | 19 |

| Case 4:  | Simulation of the codec interface circuit                   | 19 |

| Case 5:  | Simulation of the codec interface circuit integrated with a | 21 |

|          | single band FIR filter                                      |    |

| Case 6:  | Simulation and verification of debouncer3                   | 23 |

| Case 7:  | Simulation and verification of preset counter               | 25 |

| Case 8:  | Simulation and verification of user interface (user_io)     | 27 |

| Case 9:  | Test bench verification of the filter module                | 29 |

| Case 10: | Simulation verification of the RAM loaders                  | 36 |

| Case 11: | Simulation verification of the new filter                   | 38 |

| Case 12: | Test bench verification of the new filter                   | 42 |

| Case 13: | Test bench for the first temporary register                 | 45 |

| Case 14: | Test bench for the multiplier                               | 47 |

| Case 15: | Test bench for the accumulator                              | 49 |

| Case 16: | Test bench for the entire arithmetic unit                   | 51 |

| Case 17: | Debugging test bench for smart eq system                    | 53 |

|          | <del>-</del>                                                |    |

#### Case 1

The first experiment was to implement a 4-bit counter whose value is decoded through a BCD to 7-segment decoder and displayed on all on-board 7-segment displays. The circuit functioned properly with one exception. Segment 6 on one of the LED displays did not light up at all. It was discovered that in order to use the pin connected to this segment, the on-board CPLD needed to be reprogrammed. Since we do not know how to program the CPLD properly and since we do not need to use this particular LED display in our system, we did not investigate this problem any further.

#### Case 2

The second experiment was to implement the loopback circuit provided in the XStend V1.3.2 manual. The code from the manual was copied from the manual into a text file and compiled. There was, however, an error in this code that needed to be fixed which prevented a successful compilation. The signals left\_channel and right\_channel in the loopback.vhd file were only allocated 8 bits when they were expected to pass 20-bit signals. A simple correction of the signal indices corrected the problem. The code was also modified to change the active-high synchronous reset to active-low asynchronous, since an active-low synchronous pushbutton was used to generate the reset signal.

#### Case 3

To verify the operation of the loopback circuit we input an audio signal from a CD player and played the output audio from the codec on a stereo system. The loopback circuit worked properly as the audio was unaltered by the loopback circuitry.

#### Case 4

Simulation of the codec interface circuit was performed to analyze the timing requirements. The simulation waveform is included on the following page.

## Case 5

Next a single-band digital filter was integrated with the loopback circuit. The input samples from the codec are passed through the filter, then sent back to the codec for reconstruction. Simulation of the integrated circuit confirmed proper operation, however, the hardware has not yet been tested with an audio signal. The simulation waveform is included on the following page.

#### Case 6 - Test Debouncer

The test\_db test bench sends various inputs to the debouncer. This ensures that the output signals are only assigned the input values every n \* clock\_period seconds where n is equal to the constant debounce\_delay, which is assigned in user interface package file. For simulation purposes a value of 7 was used for the debounce delay. In the actual implementation a value of 1023 will be used. This shouldn't affect the operation of the user interface since speed isn't a priority.

## Case 7 - Test User I/O

The test\_io test bench is used to test the entire user interface module. The test bench models noisy pushbutton inputs to see how the interface would react. It can be seen that the noisy inputs become smooth pulses of vary width depending on the timing of the inputs. These pulses trigger the preset counter to increment or decrement. The preset counter increments or decrements only once for every pulse. The two decoders are able to convert the preset value to display the hexadecimal digit on the seven segment display and store the gain value.

## Case 8 - Test Preset Counter

The test\_preset\_counter test bench simulates the operation of the preset counter using variable pulse widths. It can be seen in the following waveform that the preset counter properly increments and decrements the preset value only oncer for every input pulse. The resulting output preset value will be stable as long as the inputs are not noisy. This requirement is fulfilled using the debouncer mechanism.

### Case 9 - Test Filter Module - Old Design

The filt\_test bench emulates the on-board stereo audio codec and generates the master clock and global reset signals. It is used to verify that the filtered samples output from the bandpass filter are correct. We begin the experiment by generating 30 random 20-bit numbers using Microsoft Excel. The numbers are then processed using MATLAB to calculate the correct filter output samples. The matlab code is provided below.

```

% this matlab program generates the output of a FIR digital filter y(n)

% given input x(n) and filter coefficents b(i)

% the input and output samples are written to xy.txt

clear:

b=[1 -6 18 101 18 -6 1];

x=[0 \ 0 \ 0 \ 0 \ 0 \ 0];

x1=[ 71 60 -86 -100 -24 22 14 119

82 0];

x2=[ 42 59 ]

6 -76 111 -66 -1 31 -117 39];

x3=[-22-52126]

99 105 121 71 92 -28 28];

xin=2^12*[x1 x2 x3];

for i=1:30,

x=[xin(i) x(1:6)];

y(i)=floor(sum(x.*b)/2048);

end

fid1=fopen('xin.txt','w');

fid2=fopen('y.txt','w');

fid3=fopen('xy.txt','w');

fprintf(fid3,'Input Samples

Output Samples\n\n');

for j=1:30,

fprintf(fid1, 'x(\%i) = \%9i\n', j-1, xin(j));

fprintf(fid2, 'y(\%i) = \%7i\n', j-1, y(j));

fprintf(fid3, 'x(\%2i) = \%9i, y(\%2i) = \%7i\n', j-1, xin(j), j-1, y(j));

end

fclose(fid1);

fclose(fid2);

fclose(fid3);

```

The matlab program generates an output file xy.txt containing two columns. This file is included on page 31. The first column contains the input sample values and the second column contains the corresponding

output sample values. The sample values are 20-bit signed numbers and are displayed in base 10 for clarity.

The randomly generated input samples were copied into the test bench file as an array of constants. The test bench loads the sample values in turn into a shift register on the rising edge of the  $lrck\_tb$  signal so that the sample values are the same for both the left and right channels. This is not necessary, it is done to simplify the verification process. The samples are then serially shifted into the filter on the rising edge of the  $sclk\_tb$  signal.

As the input samples are shifted out, the filtered samples from the previous input samples are shifted in. The filtered samples are loaded into an array on the rising edge of the  $lrck\_tb$  signal.

The bandpass filter features an 'on/off' switch that toggles the filter coefficients between two predefined sets of values. For this test case the bandpass filter (bndfilt.vhd) is set in 'off' mode. The corresponding filter is a 6th order lowpass FIR filter with a normalized cutoff frequency of 0.8 (see bndfilt.vhd).

The waveforms generated from the simulated test bench are included on the following pages. Comparison to the results listed in the *xy.txt* file confirm that the filter is executing correctly.

#### Input Samples Output Samples x(0) =290816, y(0) =142 x(1) =245760, y(1) =-732 x(2) =y(2) =-352256, 1664 x(3) =y(3) =-409600, 17334 x(4) =-98304, y(4) =12732 x(5) =90112, y(5) =-19332 x(6) =57344, y(6) =-24974 x(7) =487424, y(7) =-6434 x(8) =335872, y(8) =3848 x(9) =0, y(9) =7008 x(10) =y(10) =172032, 27266 x(11) =241664, y(11) =20338 x(12) =24576, y(12) =2368 x(13) =-311296, y(13) =9638 x(14) =y(14) =454656, 14944 x(15) =-270336, y(15) =-1368 x(16) =y(16) =-10974 -4096, x(17) =126976, y(17) =17430 x(18) =-479232, y(18) =-9054 x(19) =159744, y(19) =-1464 x(20) =-90112, y(20) =2516 x(21) =-212992, y(21) =-21074 x(22) =516096, y(22) =3376 x(23) =405504, y(23) =-4760 x(24) =y(24) =-8440 430080, x(25) =495616, y(25) =26468 x(26) =y(26) =290816, 27584 x(27) =y(27) =376832, 26846 x(28) =-114688, y(28) =28682 x(29) =114688, y(29) =21340

# Case 10 - RAM Loader

The following simulation verifies the operation of the RAM loaders used on the coefficient RAM and the sample RAM. First the coefficient RAM is loaded with 10 coefficients. Then the sample RAM is initialized by writing zero to all of the RAM locations. The annotated waveform is included on the following page.

# Case 11 - FIR Filter - New Design

The following simulation verifies the operation of the new filter design. Six audio samples are sent through the filter (three for the left channel and three for the right). The filter uses the coefficients loaded in the previous simulation. The annotated waveform is included on the following page.

#### Case 12 - Filter Test Bench

The following simulation verifies the operation of the filter. A test bench is used that simulates the codec chip. The test bench generates the appropriate clock signals and sends and recieves audio samples to and from the filter serially. The input and output samples are stored in an array for easy comparison. For the purposes of easy comparison the digital filter coefficients were set such that the output of the filter is equal to the current input sample. Essentially, the filter acts like a loopback circuit for the purposes of this test. The simulation waveform is included on the following page.

## Case 13 - Temporary Register Test Bench

The waveform on the following page illustrates how the temporary register at the input to the arithmetic unit functions. When the aload signal goes high, the gain value from the user interface is loaded in parallel to register. Otherwise, the data in the register is shifted to the right every rising edge of the clock cycle by 4 bits (the size of the gain value for each band). The least significant 4 bits of the register are sent to the output. This value is equal to the gain of the current band. The band values are therefore output from lowest band to highest band.

# Case 14 - Multiplier Test Bench

The test bench for the multiplier simply checks to make sure the output corresponds to the input values multiplied. It also checks that the output is truncated to only output 12 bits (the size of our coefficients). The waveform on the following page shows that the multiplier works porperly.

# Case 15 - Accumulator Test Bench

The waveform on the next page shows the proper operation of the accumulator section. The input value is added to the output every rising edge of the clock. The output asynchronously resets the to zero whenevery the clear signal goes high.

# Case 16 - Arithmetic Unit Test Bench

The following simulation waveforms shows the operation of the entire arithmetic unit. The accumulator adds the values of the outputs from the multiplier and sends the output to be stored in temporary register every complete run through all band gains and tap values. This system works well but could be optimized to reduce the evaluation time of each coefficient.

# Case 17 - Smart Eq Test Bench debugging

The following waveform shows how the smart eq test bench was used to debug system problems. As shown, the last element of the ceof\_register is not stored. The index element was incremented by one to allow the last coefficient to be stored. The simulation was rerun and the change managed to fix the problem. This illustrates that modular design and testing techniques ease the troubleshooting and debugging steps in the project development.

# 14 Design Hierarchy

Included on the following page is a diagram of the design hierarchy.

## 15 VHDL Code

## Index

| accumulator.vhd         | (simulated)                             | accumulates multiplier output in arithmetic unit                | 58       |

|-------------------------|-----------------------------------------|-----------------------------------------------------------------|----------|

| $arith\_unit.vhd$       | (simulated)                             | logic block used calculate the coefficient values               | 59       |

| $bcd\_decoder.vhd$      | (simulated)                             | converts binary to decimal digit on 7 segment display           | 61       |

| channel.vhd             | (simulated)                             | data channel used in codec interface module                     | 62       |

| clkgen.vhd              | (simulated)                             | clock generator for codec                                       | 66       |

| codec.vhd               | (compiled)                              | package used by codec modules                                   | 68       |

| codec_intfc.vhd         | (simulated)                             | interface module to codec                                       | 71       |

| counter.vhd             | (simulated)                             | up counter with definable wrap around value                     | 75       |

| counterd.vhd            | (simulated)                             | down counter with definable wrap around                         | 77       |

|                         | (21111111111111111111111111111111111111 | value                                                           |          |

| ${\it debouncer 3.vhd}$ | (simulated)                             | uses clock delay to scan inputs and debounce signals            | 79       |

| distram.vhd             | (compiled)                              | single port distributed RAM                                     | 80       |

| eq.vhd                  | (simulated)                             | entity containing filter, codec interface and control circuitry | 81       |

| facc.vhd                | (compiled)                              | signed accumulator                                              | 91       |

| firfilt.vhd             | (simulated)                             | FIR filter                                                      | 91<br>97 |

| firpack.vhd             | (compiled)                              |                                                                 | 92       |

| fmult.vhd               | - /                                     | package used by filter module                                   | 100      |

| fmultacc.vhd            | (simulated)                             | multiplier: inputs and output variable width                    | 100      |

|                         | (compiled)                              | multiplier accumulator for filter                               |          |

| multiplier.vhd          | (simulated)                             | multiplies filter tap by gain value in arithmetic unit          | 103      |

| preset_counter.vhd      | (simulated)                             | toggles preset values in user I/O                               | 104      |

| preset_decoder.vhd      | (simulated)                             | decodes preset values to filter gain values                     | 106      |

| ramload.vhd             | (simulated)                             | RAM loader                                                      | 107      |

| ramload1.vhd            | (simulated)                             | RAM loader                                                      | 110      |

| reg_control.vhd         | (simulated)                             | controls data flow in arithmetic unit                           | 113      |

| smart_eq.vhd            | (simulated)                             | top level entity for FPGA                                       | 115      |

| smart_eq_pack.vhd       | (compiled)                              | top level package file for smart_eq                             | 117      |

| temp_reg.vhd            | (simulated)                             | shift register that holds gain values                           | 126      |

| temp_reg2.vhd           | (simulated)                             | register that sends coefficient values to filter<br>block       | 127      |

| ugan io uhd             | (simulated)                             |                                                                 | 128      |

| $user\_io.vhd$          | (simulated)                             | user interface module                                           | 128      |

```

-- EE 552 - Project

-- Dustin Demontigny

-- March 23, 2003

-- accumulator.vhd

-- used in converting coefficients using gain value

-- Reference design taken from XST User Manual

-- http://toolbox.xilinx.com/docsan/3_1i/data/fise/xst/xst.htm

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity accumulator is

generic(input_size : integer := 12;

output_size : integer := 12);

port(clock, clr, reset : in std_logic;

data : in std_logic_vector(input_size-1 downto 0);

sum : out std_logic_vector(output_size-1 downto 0));

end accumulator;

architecture archi of accumulator is

signal temp: std_logic_vector(output_size-1 downto 0);

process (clock, clr)

if clr = '1' or reset = '0' then

temp <= (others => '0');

elsif (clock'event and clock = '1') then

temp <= temp + data;</pre>

end if;

end process;

sum <= temp;</pre>

end archi;

```

```

-- EE 552 Project

-- Dustin Demontigny

-- March 10, 2003

-- arith_unit.vhd

-- arithmetic unit to calculate filter coefficent values

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

use work.smart_eq_pack.all;

entity arith_unit is

port(clock, reset : in std_logic;

gain_register : in std_logic_vector(gain_reg-1 downto 0);

new_gain, send_coefs : in std_logic;

send_gain, new_coefs : out std_logic;

coef_register : out cramarray);

end arith_unit;

architecture mixed of arith_unit is

--signal tap_number : integer range 0 to taps*bands;

signal load_gain, shift_gain : std_logic;

signal clock_accum, clr_accum : std_logic;

signal load_coef, shift_coefs : std_logic;

signal band_gain : std_logic_vector(gain_length-1 downto 0);

signal mult_out : std_logic_vector(coef_length-1 downto 0);

signal accum_out : std_logic_vector(coef_length-1 downto 0);

signal coef_value : std_logic_vector(coef_length-1 downto 0);

begin

process(shift_gain)

variable tap_number : integer := 0;

begin

if load_gain = '1' then

tap_number := 0;

elsif shift_gain'event and shift_gain = '1' then

tap_number := tap_number + 1;

if tap_number = 4 then

tap_number := 0;

end if;

end if;

coef_value <= tap_array(tap_number);</pre>

end process;

```

```

controller : reg_control

port map(clock => clock,

reset => reset,

new_gain => new_gain,

new_coefs => new_coefs,

send_gain => send_gain,

send_coefs => send_coefs,

load_gain => load_gain,

shift_gain => shift_gain,

clock_accum => clock_accum,

clr_accum => clr_accum,

load_coef => load_coef,

shift_coefs => shift_coefs);

gain_shifter : temp_reg

generic map(input_size => gain_reg,

output_size => gain_length)

port map(clock => shift_gain,

ALOAD => load_gain,

PI => gain_register,

PO => band_gain);

multiply_coeff : multiplier

port map(A => coef_value,

B => band_gain,

RES => mult_out);

\verb"accum_ceof": \verb"accumulator""

generic map(input_size => coef_length,

output_size => coef_length)

port map(clock => clock_accum,

clr => clr_accum,

reset => reset,

data => mult_out,

sum => accum_out);

A_reg : temp_reg2

port map(clock => shift_coefs,

clr => reset,

ALOAD => load_coef,

PI => accum_out,

PO => coef_register);

end mixed;

```

```

-- EE 552 - Project

-- Dustin Demontigny

-- February 11, 2003

-- bcd_decoder.vhd

-- converts binary to 7 segment display

library ieee;

use ieee.std_logic_1164.all;

-- digit values are assigned in package file

use work.smart_eq_pack.all;

entity bcd_decoder is

port(

binary_input : in std_logic_vector(bits-1 downto 0);

segment_output : out std_logic_vector(led_segments-1 downto 0));

end bcd_decoder;

architecture struct of bcd_decoder is

-- select the digit that corresponds to the binary input

with binary_input select

segment_output <=

digit_1 when "0000",

digit_2 when "0001",

digit_3 when "0010",

digit_4 when "0011",

digit_5 when "0100",

digit_6 when "0101",

digit_7 when "0110",

digit_8 when "0111",

digit_9 when "1000",

digit_0 when "1001",

digit_A when "1010",

digit_b when "1011",

digit_C when "1100",

digit_d when "1101",

digit_E when "1110",

digit_F when "1111",

digit_e when others; -- displays "e" for error

end struct;

```

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

use work.codec.all;

entity channel is

generic

(

DAC_WIDTH

positive := 20;

ADC_WIDTH

positive := 20

:

);

port

-- interface I/O signals

-- clock input

clk

: in std_logic;

-- synchronous active-high reset

reset

: in std_logic;

: in std_logic;

chan_on

: in std_logic_vector(5 downto 0);

bit_cntr

subcycle_cntr : in std_logic_vector(1 downto 0);

chan_sel : in std_logic; -- select L/R channel for read/write

-- read from the codec ADC

: in std_logic;

-- write to the codec DAC

wr

: in std_logic;

: out std_logic_vector(ADC_WIDTH-1 downto 0); -- ADC output

adc_out

: in std_logic_vector(DAC_WIDTH-1 downto 0); -- DAC input

dac_in

adc_out_rdy : out std_logic; -- ADC output is ready to be read

adc_overrun : out std_logic; -- ADC overwritten before being read

dac_in_rdy : out std_logic; -- DAC input is ready to be written

dac_underrun : out std_logic;

-- input to DAC arrived late

-- codec chip I/O signals

: out std_logic;

-- serial output to codec DAC

sdin

sdout

: in std_logic

-- serial input from codec ADC

);

end channel;

architecture channel_arch of channel is

signal dac_shfreg : std_logic_vector(DAC_WIDTH-1 downto 0);

: std_logic; -- DAC shift register is empty

signal dac_empty

: std_logic; -- the DAC channel has been written

signal dac_wr

signal dac_wr_nxt : std_logic;

-- the DAC channel has been written

signal dac_in_rdy_int : std_logic;

-- internal version of dac_in_rdy

signal adc_shfreg : std_logic_vector(ADC_WIDTH-1 downto 0);

signal adc_full

: std_logic;

-- ADC shift register is full

signal adc_rd

: std_logic;

-- the ADC channel has been read

signal adc_rd_nxt

: std_logic; -- the ADC channel has been read

```

```

signal adc_out_rdy_int : std_logic; -- internal version adc_out_rdy

-- receives data from codec ADC

process(clk)--, chan_on, subcycle_cntr, bit_cntr, adc_shfreg, sdout)

begin

if(clk'event and (clk = YES)) then

if(reset = '1') then

adc_shfreg <= (others => '0');

adc full

\leq NO;

elsif((chan_on = YES) and (subcycle_cntr = 2)) then

if(bit_cntr < ADC_WIDTH-1) then</pre>

adc_full

<= NO;

adc_shfreg <= adc_shfreg(ADC_WIDTH-2 downto 0) & sdout;</pre>

elsif(bit_cntr = ADC_WIDTH-1) then

adc_full <= YES;</pre>

adc_shfreg <= adc_shfreg(ADC_WIDTH-2 downto 0) & sdout;</pre>

end if;

end if;

end if;

end process;

adc_out

<= adc_shfreg;

-- handle reading of ADC data from codec interface

adc_rd_nxt

<= YES when (adc_full = YES and chan_sel = YES and rd = YES) or

(adc_full = YES and adc_rd = YES)

else NO;

read_adc :

process(clk)--, adc_rd_nxt)

if(clk'event and clk = '1') then

if(reset = YES) then

adc_rd <= NO;

else

adc_rd <= adc_rd_nxt;</pre>

end if;

end if;

end process;

-- ADC data is ready if register is full and hasn't been read yet

adc_out_rdy_int <= YES when adc_full = YES and adc_rd = NO else NO;

<= adc_out_rdy_int;</pre>

adc_out_rdy

-- detect and signal overwriting of data from the codec ADC channels

detect_adc_overrun : process(clk)--, bit_cntr, chan_on, adc_out_rdy_int)

begin

```

```

if(clk'event and clk = '1') then

if(reset = YES) then

adc_overrun <= NO;</pre>

elsif(bit_cntr = 1 and chan_on = YES and adc_out_rdy_int = YES) then

adc_overrun <= YES;</pre>

end if;

end if;

end process;

-- transmits data to codec DAC

tx_dac : process(clk)--, chan_on, subcycle_cntr, bit_cntr, dac_shfreg)

begin

if(clk'event and clk = '1') then

if(reset = YES) then

dac_shfreg <= (others => '0');

<= YES;

dac_empty

elsif(chan_sel = YES and wr = YES) then

dac_shfreg <= dac_in;</pre>

elsif(chan_on = YES and subcycle_cntr = 2) then

if(bit_cntr < DAC_WIDTH-1) then</pre>

dac_empty <= NO;</pre>

dac_shfreg <= dac_shfreg(DAC_WIDTH-2 downto 0) & '0';</pre>

elsif(bit_cntr = DAC_WIDTH-1) then

dac_empty <= YES;</pre>

dac_shfreg <= dac_shfreg(DAC_WIDTH-2 downto 0) & '0';</pre>

end if;

end if;

end if;

end process;

-- output the serial data to the SDIN pin of the codec DAC

sdin <= dac_shfreg(DAC_WIDTH-1) WHEN chan_on = YES ELSE '0';</pre>

-- handle writing of DAC data from codec interface

dac_wr_nxt <= YES WHEN (dac_empty = YES AND chan_sel = YES AND wr = YES) OR

(dac_empty = YES AND dac_wr = YES) ELSE NO;

write_dac :

PROCESS(clk)--, dac_wr_nxt)

BEGIN

IF(clk'event AND clk = '1') THEN

IF(reset = YES) THEN

dac_wr <= NO;</pre>

ELSE

dac_wr <= dac_wr_nxt;</pre>

END IF;

```

```

END IF;

END PROCESS;

-- DAC is ready if register is empty and hasn't been written yet

dac_in_rdy_int <= YES WHEN dac_empty = YES AND dac_wr = NO ELSE NO;</pre>

<= dac_in_rdy_int;</pre>

dac_in_rdy

-- detect and signal underflow of data to the codec DAC channels

detect_dac_underrun :

PROCESS(clk)--, bit_cntr, chan_on, dac_in_rdy_int)

BEGIN

IF(clk'event AND clk = '1') THEN

IF(reset = YES) THEN

dac_underrun <= NO;</pre>

ELSIF(bit_cntr = 1 AND chan_on = YES AND dac_in_rdy_int = YES) THEN

dac_underrun <= YES;</pre>

END IF;

END IF;

END PROCESS;

END channel_arch;

```

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

use work.codec.all;

entity clkgen is

generic

CHANNEL_DURATION: positive := 128 -- must be 128

);

port

(

-- interface I/O signals

clk

: in std_logic; -- clock input

: in std_logic; -- synchronous active-high reset

reset

-- codec chip clock signals

mclk

: out std_logic; -- master clock output to codec

: out std_logic; -- serial data clock to codec

sclk

lrck

: out std_logic; -- left/right codec channel select

: out std_logic_vector(5 downto 0);

bit_cntr

subcycle_cntr : out std_logic_vector(1 downto 0)

);

end clkgen;

architecture clkgen_arch of clkgen is

signal lrck_int : std_logic;

signal seq : std_logic_vector(7 downto 0);

begin

gen_clock : process(clk)--, seq, lrck_int)

if (clk'event and clk = '1') then

if(reset = YES) then

-- synchronous reset

<= (others => '0');

seq

lrck_int <= left;</pre>

-- start with left channel of codec

elsif(seq = CHANNEL_DURATION-1) then

<= (others => '0'); -- reset sequencer every channel period

lrck_int <= not(lrck_int);</pre>

-- toggle channel sel every period

else

seq

\leq seq+1;

lrck_int <= lrck_int;</pre>

END IF;

END IF;

END PROCESS;

<= lrck_int;

-- output the channel selector to the codec

lrck

mclk

<= clk;

-- codec master clock equals input clock

```

```

sclk <= seq(1); -- serial data shift clock = 1/4 master clock

bit_cntr <= seq(7 DOWNTO 2);

subcycle_cntr <= seq(1 DOWNTO 0);

END clkgen_arch;</pre>

```

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.std_logic_unsigned.all;

package codec is

constant yes

: std_logic := '1';

: std_logic := '0';

constant no

constant ready : std_logic := '1';

constant overrun : std_logic := '1';

constant underrun : std_logic := '1';

constant left : std_logic := '0';

constant right : std_logic := '1';

component clkgen

generic

(

CHANNEL_DURATION: positive:= 128 -- must be 128

);

port

(

-- interface I/O signals

clk : in std_logic;

-- clock input

reset : in std_logic;

-- synchronous active-high reset

-- codec chip clock signals

mclk

: out std_logic; -- master clock output to codec

: out std_logic; -- serial data clock to codec

sclk

: out std_logic; -- left/right codec channel select

bit_cntr : out std_logic_vector(5 downto 0);

subcycle_cntr : out std_logic_vector(1 downto 0)

);

end component;

component channel

generic

(

DAC_WIDTH : positive := 20;

ADC_WIDTH : positive := 20

);

port

(

-- interface I/O signals

: in std_logic; -- clock input

reset

: in std_logic; -- synchronous active-high reset

: in std_logic;

chan on

bit_cntr

: in std_logic_vector(5 downto 0);

```

```

subcycle_cntr : in std_logic_vector(1 downto 0);

chan_sel : in std_logic; -- select L/R channel for read/write

rd

: in std_logic; -- read from the codec ADC

: in std_logic; -- write to the codec DAC

: out std_logic_vector(ADC_WIDTH-1 downto 0); -- ADC output

adc_out

: in std_logic_vector(DAC_WIDTH-1 downto 0); -- DAC input

dac_in

adc_out_rdy : out std_logic; -- ADC output is ready to be read

adc_overrun : out std_logic; -- ADC overwritten before being read

: out std_logic; -- DAC input is ready to be written

dac_in_rdy

dac_underrun : out std_logic; -- input to DAC arrived late

-- codec chip I/O signals

: out std_logic; -- serial output to codec DAC

sdin

: in std_logic -- serial input from codec ADC

sdout

);

end component;

component codec_intfc

generic

(

DAC_WIDTH

:

positive := 20;

ADC_WIDTH

positive := 20;

:

CHANNEL_DURATION :

positive := 128 -- must be 128

);

port

(

-- interface I/O signals

: in std_logic; -- clock input

clk

: in std_logic; -- synchronous active-high reset

reset

: in std_logic; -- select L/R channel for read/write

lrsel

: in std_logic; -- read from the codec ADC

rd

: in std_logic; -- write to the codec DAC

wr

: out std_logic_vector(ADC_WIDTH-1 downto 0); -- L ADC

ladc_out

: out std_logic_vector(ADC_WIDTH-1 downto 0); -- R ADC

radc_out

: IN std_logic_vector(DAC_WIDTH-1 DOWNTO 0); -- left DAC

ldac_in

: IN std_logic_vector(DAC_WIDTH-1 DOWNTO 0); -- right DAC

rdac_in

ladc_out_rdy

: OUT std_logic; -- left ADC output ready to read

radc_out_rdy

: OUT std_logic; -- right ADC output ready to read

: OUT std_logic; -- ADC overwritten before read

adc_overrun

: OUT std_logic; -- left DAC in ready to be written

ldac_in_rdy

: OUT std_logic; --right DAC in ready to be written

rdac_in_rdy

: OUT std_logic; -- DAC did not receive data in time

dac_underrun

: out std_logic_vector(5 downto 0);

bit_cntr

-- codec chip I/O signals

mclk

: OUT std_logic; -- master clock output to codec

sclk

: OUT std_logic; -- serial data clock to codec

```

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

use work.codec.all;

entity codec_intfc is

generic

(

DAC_WIDTH

positive := 20;

:

positive := 20;

positive := 128 -- must be 128

ADC WIDTH

:

CHANNEL_DURATION :

);

port

-- interface I/O signals

: in std_logic; -- clock input

: in std_logic; -- synchronous active-high reset

reset

lrsel

: in std_logic; -- select L/R channel for read/write

rd

: in std_logic; -- read from the codec ADC

: in std_logic; -- write to the codec DAC

: out std_logic_vector(ADC_WIDTH-1 downto 0); -- L ADC

ladc_out

radc_out

: out std_logic_vector(ADC_WIDTH-1 downto 0); -- R ADC

ldac_in

: in std_logic_vector(DAC_WIDTH-1 downto 0); -- left DAC

: in std_logic_vector(DAC_WIDTH-1 downto 0); -- right DAC

rdac_in

ladc_out_rdy

: out std_logic; -- left ADC output ready to read

radc_out_rdy : out std_logic; -- right ADC output ready to read

: out std_logic; -- ADC overwritten before read

adc overrun

: out std_logic; -- left DAC in ready to be written

ldac_in_rdy

: out std_logic; --right DAC in ready to be written

rdac_in_rdy

: out std_logic; -- DAC did not receive data in time

dac_underrun

bit_cntr

: out std_logic_vector(5 downto 0);

-- codec chip I/O signals

: out std_logic; -- master clock output to codec

mclk

sclk

: out std_logic; -- serial data clock to codec

lrck

: out std_logic; -- left/right codec channel select

: out std_logic; -- serial output to codec DAC

sdin

sdout

: in std_logic -- serial input from codec ADC

);

end codec_intfc;

architecture codec_intfc_arch of codec_intfc is

signal mclk_int : std_logic; -- internal codec master clock

-- internal L/R codec channel select

signal lrck_int

: std_logic;

signal sclk_int

: std_logic;

-- internal codec data shift clock

signal bit_cntr_int : std_logic_vector(5 downto 0);

```

```

signal subcycle_cntr : std_logic_vector(1 downto 0);

: std_logic;

signal 1sdin

signal rsdin

: std_logic;

signal ladc_overrun : std_logic;

signal radc_overrun : std_logic;

signal ldac_underrun : std_logic;

signal rdac_underrun : std_logic;

signal lchan_sel : std_logic;

signal rchan_sel : std_logic;

signal lchan_on : std_logic;

signal rchan_on : std_logic;

begin

u0 : clkgen

generic map

CHANNEL_DURATION => CHANNEL_DURATION

)

port map

(

=> clk,

clk

=> reset,

reset

mclk

=> mclk_int,

sclk

=> sclk_int,

lrck

=> lrck_int,

bit_cntr => bit_cntr_int,

subcycle_cntr => subcycle_cntr

);

lrck

<= not(lrck_int);

-- invert for inverter in XStend V1.3

mclk

<= not(mclk_int);

<= not(sclk_int);

sclk

bit_cntr <= bit_cntr_int;</pre>

lchan_sel <= YES when lrsel = left</pre>

else NO;

lchan_on <= YES when lrck_int = left else NO;</pre>

u_left : channel

generic map

DAC_WIDTH

=> DAC_WIDTH,

ADC_WIDTH

=> ADC_WIDTH

)

port map

clk

=> clk,

reset

=> reset,

```

```

chan_on

=> lchan_on,

bit_cntr

=> bit_cntr_int,

subcycle_cntr => subcycle_cntr,

chan_sel

=> lchan_sel,

=> rd,

rd

wr

=> wr,

=> ladc_out,

adc_out

\mathtt{dac}\mathtt{\_in}

=> ldac_in,

adc_out_rdy => ladc_out_rdy,

adc_overrun

=> ladc_overrun,

dac_in_rdy

=> ldac_in_rdy,

dac_underrun => ldac_underrun,

sdin

=> lsdin,

sdout

=> sdout

);

rchan_sel <= YES WHEN lrsel = RIGHT</pre>

ELSE NO;

rchan_on <= YES WHEN lrck_int = RIGHT ELSE NO;</pre>

u_right : channel

GENERIC MAP

DAC_WIDTH

=> DAC_WIDTH,

ADC_WIDTH

=> ADC_WIDTH

)

PORT MAP

clk

=> clk,

reset

=> reset,

chan_on

=> rchan_on,

=> bit_cntr_int,

bit_cntr

subcycle_cntr => subcycle_cntr,

chan_sel

=> rchan_sel,

rd

=> rd,

wr

=> wr,

=> radc_out,

adc_out

\mathtt{dac}\mathtt{\_in}

=> rdac_in,

adc_out_rdy => radc_out_rdy,

adc_overrun => radc_overrun,

dac_in_rdy

=> rdac_in_rdy,

dac_underrun => rdac_underrun,

sdin

=> rsdin,

sdout

=> sdout

);

```

```

counter.vhd

-- Name:

-- Author: David Bull

-- Description:

-- Up counter with definable wrap around value

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity counter is

generic (

width

: integer := 4;

wrapval : integer := 2**4);

port (

: in std_logic;

clk

en : in std_logic;

rst : in std_logic;

count : out std_logic_vector(width-1 downto 0));

end counter;

architecture countarch of counter is

constant wrapvalue : std_logic_vector(width-1 downto 0)

:= conv_std_logic_vector(wrapval,width);

signal cnt : std_logic_vector(width-1 downto 0);

begin -- countarch

clockcount: process (clk)

begin -- process clockcount

if clk'event and clk = '1' then

if rst = '1' then

cnt <= (others => '0');

elsif en = '1' then

if cnt = wrapval then

cnt <= (others => '0');

else

cnt <= cnt + 1;</pre>

end if;

end if;

end if;

```

```

end process clockcount;

count <= cnt;

end countarch;</pre>

```

```

counterd.vhd

-- Name:

-- Author: David Bull

-- Description:

-- Down counter with definable wrap around value.

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity counterd is

generic (

width

: integer := 4;

wrapval : integer := 9);

port (

: in std_logic;

clk

en : in std_logic;

rst : in std_logic;

count : out std_logic_vector(width-1 downto 0));

end counterd;

architecture countdarch of counterd is

constant wrapvalue : std_logic_vector(width-1 downto 0)

:= conv_std_logic_vector(wrapval,width);

constant zero : std_logic_vector(width-1 downto 0)

:= conv_std_logic_vector(0,width);

signal cnt : std_logic_vector(width-1 downto 0);

begin -- countdarch

clockcount: process (clk)

begin -- process clockcount

if clk'event and clk = '1' then

if rst = '1' then

cnt <= (others => '0');

elsif en = '1' then

if cnt = zero then

cnt <= wrapvalue;</pre>

else

cnt <= cnt - 1;</pre>

end if;

```

```

end if;

end if;

end process clockcount;

count <= cnt;

end countdarch;</pre>

```

```

-- EE 552 - Project

-- Dustin Demontigny

-- February 11, 2003

-- debouncer3.vhd

-- Debounce mechanism for push buttons

-- uses D-flip flop with enable configuration

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

use work.smart_eq_pack.all;

entity debouncer3 is

port(pb_input : in std_logic_vector(pb_number-1 downto 0);

clock : in std_logic;

db_output : out std_logic_vector(pb_number-1 downto 0));

end debouncer3;

architecture DFF of debouncer3 is

begin

process (clock)

variable count : integer := 0;

if clock'event and clock = '1' then

count := count + 1; -- counts the number of clock cycles

if count = debounce_delay then-- when desired delay is reached

db_output <= pb_input; -- inputs are mapped to outputs</pre>

count := 0;

-- and counting begins from zero

end if;

end if;

end process;

end DFF;

```

```

-- Name:

distram.vhd

-- Author: David Bull

-- Description:

Single port distributed RAM

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity rambank is

generic (

portwidth : integer := 20;

addwidth : integer := 5);

port (

clk : in std_logic;

we : in std_logic;

a : in std_logic_vector(addwidth-1 downto 0);

di : in std_logic_vector(portwidth-1 downto 0);

do : out std_logic_vector(portwidth-1 downto 0));

end rambank;

architecture ramarch of rambank is

type ram_type is array (2**addwidth-1 downto 0) of

std_logic_vector (portwidth-1 downto 0);

signal RAM : ram_type;

begin

process (clk)

begin

if (clk'event and clk = '1') then

if (we = '1') then

RAM(conv_integer(a)) <= di;</pre>

end if;

end if;

end process;

do <= RAM(conv_integer(a));</pre>

end ramarch;

```

```

-- Name:

eq.vhd

-- Author: David Bull

-- Date: March 2003

-- Description:

This is the entity containing the digital filter, codec

interface, RAM loaders and control circuitry

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use work.firpack.all;

use work.codec.all;

entity eq is

generic (

cwidth

: integer := coeffwidth;

: integer := samplewidth;

swidth

caddwidth : integer := coeffaddwidth;

saddwidth : integer := sampleaddwidth;

filtorder : integer := filterorder);

port (

clk

: in std_logic;

rst : in std_logic;

sdout : in std_logic;

sdin : out std_logic;

mclk : out std_logic;

sclk : out std_logic;

lrck : out std_logic);

end eq;

architecture eqarch of eq is

signal ladc_out : std_logic_vector(swidth-1 downto 0);

signal radc_out : std_logic_vector(swidth-1 downto 0);

signal ladc_out_rdy : std_logic;

signal radc_out_rdy : std_logic;

signal ldac_in

: std_logic_vector(swidth-1 downto 0);

signal rdac_in

: std_logic_vector(swidth-1 downto 0);

signal ldac_in_rdy : std_logic;

signal rdac_in_rdy : std_logic;

signal wr

: std_logic;

signal adc_overrun : std_logic;

signal dac_underrun : std_logic;

```

```

signal coefframin : std_logic_vector(cwidth-1 downto 0);

signal sampleramin : std_logic_vector(swidth-1 downto 0);

signal coeffadden : std_logic;

signal sampleadden : std_logic;

signal coeffwe

: std_logic;

signal samplewe

: std_logic;

signal coeffrst

: std_logic;

signal samplerst

: std_logic;

signal sampleramin_int : std_logic_vector(swidth-1 downto 0);

signal coeffadden_int : std_logic;

signal sampleadden_int : std_logic;

signal coeffwe_int : std_logic;

signal samplewe_int : std_logic;

signal coeffrst_int : std_logic;

signal samplerst_int : std_logic;

signal sampleramin_ext : std_logic_vector(swidth-1 downto 0);

signal coeffadden_ext : std_logic;

signal sampleadden_ext : std_logic;

signal coeffwe_ext : std_logic;

signal samplewe_ext : std_logic;

signal coeffrst_ext : std_logic;

signal samplerst_ext : std_logic;

signal coeffintext : std_logic;

signal sampleintext : std_logic;

signal clracc : std_logic;

signal accen : std_logic;

signal poscount

: std_logic_vector(7 downto 0);

signal poscount_coeff : std_logic_vector(7 downto 0);

signal poscount_sample : std_logic_vector(7 downto 0);

signal posen

: std_logic;

signal posrst

: std_logic;

signal posen_eq

: std_logic;

: std_logic;

signal posrst_eq

signal posen_coeff

: std_logic;

signal posrst_coeff : std_logic;

signal posen_sample : std_logic;

signal posrst_sample : std_logic;

signal posen_ram

: std_logic;

signal posrst_ram

: std_logic;

```

```

signal lrsample_int : std_logic;

signal lrsample_coeff : std_logic;

signal lrsample_sample : std_logic;

signal lrsample_ram : std_logic;

signal lrsel1

: std_logic;

signal samplepos

: std_logic_vector(6 downto 0);

signal samplepos_coeff : std_logic_vector(6 downto 0);

signal samplepos_sample : std_logic_vector(6 downto 0);

constant forderp1 : std_logic_vector(6 downto 0)

:= conv_std_logic_vector(filtorder+1, 7);

constant forderp2 : std_logic_vector(6 downto 0)

:= conv_std_logic_vector(filtorder+2, 7);

constant forderp3 : std_logic_vector(6 downto 0)

:= conv_std_logic_vector(filtorder+3, 7);

constant zero : std_logic_vector(6 downto 0)

:= conv_std_logic_vector(0, 7);

constant one : std_logic_vector(6 downto 0)

:= conv_std_logic_vector(1, 7);

signal cont_req_coeff : std_logic;

signal cont_rel_coeff : std_logic;

signal cont_ack_coeff : std_logic;

signal cont_req_sample : std_logic;

signal cont_rel_sample : std_logic;

signal cont_ack_sample : std_logic;

signal rambusy : std_logic;

signal coefframidle : std_logic;

signal sampleramidle : std_logic;

signal data_in_coeff

: cramarray;

signal data_in_rdy_coeff : std_logic;

signal data_in_ack_coeff : std_logic;

: sramarray;

signal data_in_sample

signal data_in_rdy_sample : std_logic;

signal data_in_ack_sample : std_logic;

signal prev_rst : std_logic;

signal pres_rst : std_logic;

```

```

begin -- eqarch

filter: firfilt

generic map (

cwidth => cwidth,

=> swidth,

swidth

caddwidth => caddwidth,

saddwidth => saddwidth,

filtorder => filtorder)

port map (

clk

=> clk,

coefframin => coefframin,

sampleramin => sampleramin,

coeffadden => coeffadden,

sampleadden => sampleadden,

coeffwe

=> coeffwe,

samplewe

=> samplewe,

=> coeffrst,

coeffrst

samplerst => samplerst,

clracc

=> clracc,

accen

=> accen,

lrsample

=> lrsample,

filtout

=> filtout);

codecintfc: codec_intfc

generic map (

DAC_WIDTH

=> swidth,

ADC_WIDTH

=> swidth,

CHANNEL_DURATION => 128)

port map (

=> clk,

clk

=> rst,

reset

lrsel

=> lrsample,

=> samplewe,

rd

wr

=> wr,

ladc_out

=> ladc_out,

radc_out => radc_out,

ldac_in

=> ldac_in,

=> rdac_in,

rdac_in

ladc_out_rdy => ladc_out_rdy,

radc_out_rdy => radc_out_rdy,

adc_overrun => adc_overrun,

ldac_in_rdy => ldac_in_rdy,

rdac_in_rdy => rdac_in_rdy,

dac_underrun => dac_underrun,

```

```

mclk

=> mclk,

sclk

=> sclk,

=> lrck,

lrck

sdin

=> sdin,

sdout

=> sdout);

sampleposcounter: counter

generic map (

width => 8,

wrapval => 2**8)

port map (

clk

=> clk,

en

=> posen,

rst => posrst,

count => poscount);

sampleposcounter2: counter

generic map (

width \Rightarrow 8,

wrapval => 2**8)

port map (

clk => clk,

=> posen_coeff,

rst => posrst_coeff,

count => poscount_coeff);

sampleposcounter3: counter

generic map (

width \Rightarrow 8,

wrapval => 2**8)

port map (

clk => clk,

en

=> posen_sample,

rst => posrst_sample,

count => poscount_sample);

rload: ramload

generic map (

=> cwidth,

swidth

filtorder => filtorder)

port map (

clk

=> clk,

=> rst,

rst

=> data_in_coeff,

data_in

data_in_rdy => data_in_rdy_coeff,

```

```

data_in_ack => data_in_ack_coeff,

data_out => coefframin,

we

=> coeffwe_ext,

adden

=> coeffadden_ext,

=> coeffrst_ext,

addrst

=> posen_coeff,

posen

=> posrst_coeff,

posrst

cont_req => cont_req_coeff,

=> cont_ack_coeff,

cont_ack

cont_rel => cont_rel_coeff,

samplepos => samplepos_coeff);

rload1: ramload1

generic map (

swidth

=> swidth,

filtorder => filtorder)

port map (

clk

=> clk,

rst

=> rst,

data_in => data_in_sample,

data_in_rdy => data_in_rdy_sample,

data_in_ack => data_in_ack_sample,

data_out => sampleramin_ext,

=> samplewe_ext,

we

adden

=> sampleadden_ext,

addrst

=> samplerst_ext,

=> posen_sample,

posen

=> posrst_sample,

posrst

cont_req => cont_req_sample,

cont_ack => cont_ack_sample,

cont_rel => cont_rel_sample,

=> lrsample_sample,

lrsample

samplepos => samplepos_sample);

<= poscount(6 downto 0);</pre>

samplepos

samplepos_coeff <= poscount_coeff(6 downto 0);</pre>

samplepos_sample <= poscount_sample(6 downto 0);</pre>

coeffadden <= coeffadden_int when coeffintext = '0'</pre>